# Charge Nonconservative Ac Modeling of Fgmosfet

RAS. B.H. Aliyev, prof.RAE. Z.H. Aliyev

zaakirakademik@mail.ru

## Abstract

This paper studies the Floating- Gate MOSFET (FGMOSFET) for its importance in biomedical engineering and many modern low-power applications. A practical model for FGMOSFET is highly needed to be used in circuits simulators. In this work, a spice model for FGMOSFET is introduced and can be inserted in any circuit simulator such as Spector and various SPICE programs (i.e. HSPICE, WinSPICE, etc.). Firstly, the parasitic capacitances needed for FGMOSFET is revised for 0.13um CMOS technology. Secondly, a model for both mutual and output transconductance is represented. The model is based on n-channel FGMOSFET and valid from linear to saturation regions. The model considers velocity saturation as short channel effect and bulk charge due to drain-to-source voltage as second order effect. The results were verified by the spice simulation BSIM3v3 model in Cadence. The model is not a charge conservative.

Keywords— FGMOSFET Model; CAD tools; Devices Modeling; Nano Electronics; Spice Circuit Simulation.

# I. INTRODUCTION

COMPUTER AIDED DESIGN (CAD) TOOLS IS CONSIDERED THE BASIC REFERENCE TO CIRCUIT SIMULATION NOWADAYS. IT HELPS RESEARCHERS AND INDUSTRY PEOPLE TO FIGURE OUT THE CHARACTERISTIC FOR THEIR DEVICES IN AN ACCURATE WAY.

FLOATING-GATE MOS DEVICES HAVE BEEN BELIEVED AS ONE OF THE DOMINANT STRUCTURES TO EXTEND THE SCALING LIMIT DUE TO THE INCREASING OF THRESHOLD VOLTAGE CONTROL. THE FGMOS DEVICES ATTRACT THE RESEARCHERS WORKING ON ANALOG DESIGN DUE TO ITS ELECTRICAL CHARACTERISTICS FOR DATA COMPUTATION AND LOW POWER DISSIPATION. MOREOVER, THE FGMOS DEVICES ARE GOOD DEVICES FOR CONTROLLING THRESHOLD VOLTAGE AND ENHANCING THE CHARGING AND DISCHARGING TIME THROUGH THE COUPLING CAPACITANCE VALUE CONTROL. THE FGMOS DEVICES FOLLOW THE SAME CMOS TECHNOLOGY AND DOES NOT NEED A SPECIFIC FABRICATION PROCESS [1].

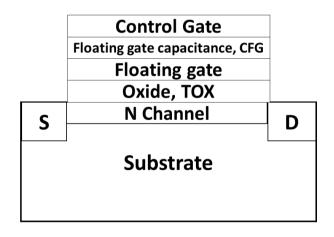

## Fig. 1 Structure of FGMOSFET device.

Shows the structure of FGMOSFET device where  $T_{OX}$  is the thickness of oxide between floating gate and channel and  $C_{FG}$  is the capacitance between the control gate and floating gate.

Floating Gate MOSFET (FGMOSFET) is found in many circuits like Flash and EEPROM Memories, low-power circuits [2], many biomedical Sensors like DeFET [3] and photonics circuits [4].

This paper represents a practical model for FGMOSFET to be used in future for circuit and device simulation. The parasitic capacitances are revised [5]. Then a mathematical model for mutual and output transconductance is introduced. Finally, a comparison between the proposed model and BSIM3v3 model [6] in Cadence is discussed. The simulation method [7] is the same as used in [5]. The proposed model is not a charge conservative, unlike BSIM3v3, but is more flexible to use as it doesn't depend on parameter extraction as in the other.

#### **II. PARASITIC CAPACITANCES**

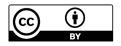

From [5], the parasitic capacitances, C<sub>fs</sub> and C<sub>fd</sub>, in linear and saturation regions where found to be in the form:

(2)

(1)

Where C<sub>fs</sub> and C<sub>fd</sub> are the parasitic capacitances between floating gate and Source and Drain, respectively.

The parameters in the two equations are as following:

1) *K*, called the conductivity of FGMOSFET

$k = (WC_{ox}/\alpha_c)$

### (3)

Where W is the transistor width,  $C_{ox}$  is the oxide capacitance between the floating gate and channel and  $\alpha_c$  is the capacitance coupling coefficient between the floating gate, and control gate.

- 2)  $E_c$  the critical electric field.

- *3) L* is the transistor length.

- 4) V<sub>FB</sub> is the flat band voltage due to nonideality of the MOS capacitor.

- 5)  $\Delta V_{th}$  term represents the Drain Induced Barrier Lowering (DIBL) effect from BSIM4 [8].

- 6) Other terms represents the voltage of the structure as discussed in [5].

The parasitic capacitance can be used to derive the DC model of FGMOSFET as in [5] and the AC model as discussed in next section.

#### III. TRANSCONDUCTANCE MODEL

The main elements which are needed in AC modeling of a transistor are the parasitic capacitances and transconductances. The mutual conductance  $g_m$  and output (drain) conductance  $g_d$  can be easily derived by:

$$g_m = \frac{\partial I_D}{\partial V_{GS}} | V_{DS} |$$

(4)

$g_{d} = \frac{\partial I_{D}}{\partial V_{DS}} | V_{GS}$

(5)

Where  $I_D$  is the drain current derived in [5] and  $V_{GS}$  and  $V_{DS}$  are control gate and Drain to Source voltages, respectively.

The results of this partial differentiation are:

$$g_m = \frac{\frac{W\mu_{ns}C_{ox}}{L}V_{Ds}}{V_c}$$

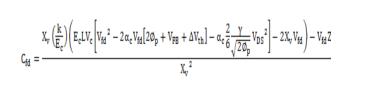

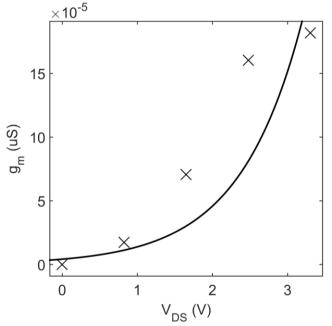

Fig. 2 DC analysis for output transconductance of FGMOSFET in siemens vs. drain to source voltage, solid line is the model and symbol is the BSIM3v3 model in simulator. The control gate voltage equals **2.5V**.

(7)

$$g_{d} = \frac{\frac{W\mu_{ng}C_{ox}}{\alpha_{c}L} \left[ -\alpha_{c}V_{GS} + X_{c}V_{DS} + \alpha_{c}(V_{TO} + V_{FB}) + \frac{X_{c}}{2E_{c}L}V_{DS}^{2} \right]}{V_{c}^{2}}$$

Where  $\mu_{ns}$ ,  $V_c$ ,  $V_{TO}$  are the effective surface mobility of electrons [9], the effect of the velocity saturation [5] and threshold voltage at zero drain bias [10]

The term  $X_C$  is expressed as:

$$X_c = \alpha_c \frac{\Delta V_{\rm th}}{V_{\rm DS}} + 1 - 2\alpha_{\rm d}$$

(8)

Where  $\alpha_d$  is the capacitance coupling coefficient between the floating gate and drain.  $\frac{\Delta v_{th}}{v_{DS}}$  represent a constant term for DIBL effect depends on channel length, doping of substrate,

oxide thickness and electric permittivity of oxide and silicon.

As shown in the transconductance equations, they need the values of the parasitic capacitances derived in [5].

#### **IV. RESULTS VERIFICATION**

Fig. 2 represents the comparison between the proposed model and the BSIM3v3 simulation in DC simulation in Cadence for output conductance.

The parasitic capacitance values in [5] were used to draw the model of the transconductances. Then simulation for FGMOSFET in Cadence were done. Finally, both model and simulation were put in one figure for comparison

There is a difference between the proposed model and BSIM3v3 and this is because the proposed model is a

charge nonconservative

Fig. 3 DC analysis for mutual transconductance of FGMOSFET in siemens vs. drain to source voltage, solid line is the model and symbol is the BSIM3v3 model in simulator. The control gate voltage equals 2.5V.

model while BSIM3v3 is not. The percentage of error in best cases is 5%.

Fig. 3 shows the comparison between the proposed model and the BSIM3v3 simulation in DC simulation in Cadence for mutual conductance.

All parameters used are stated in Table. 1.

TABLE I. PARAMETERS USED

| Paramet<br>er                                       | Symbol          | Value  |

|-----------------------------------------------------|-----------------|--------|

| Oxide<br>thicknes                                   | T <sub>OX</sub> | 3 nm   |

| Relative<br>permittiv<br>ity of<br>silicon<br>oxide | Eroz            | 3.9    |

| Transisto<br>r width                                | W               | 1 um   |

| Transisto<br>r length                               | L               | 340 nm |

| Floating<br>gate<br>capacita<br>nce                 | C <sub>FG</sub> | 2.4 fF |

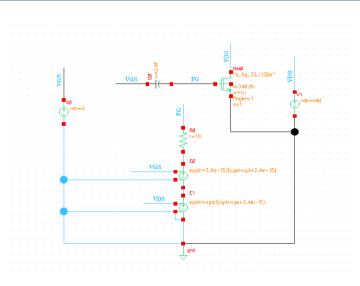

The same simulation method [7] for FGMOSFET that used in [5] is used here, see Fig. 4.

## CONCLUSION

In this work, mathematical modeling of transconductances of FGMOSFET is stated. The model is practical and can be used in many circuit simulators. The main disadvantage of the proposed model is that it is charge independent model. So, the model is not very accurate with error percentage of 5% in

### Fig. 4 Cadence schematic diagram for simulating FGMOSFET with BSIM3v3 model.

most values along the sweep with voltage. The error percentage is also bad for using less efficient mobility model.

Future intention is to adapt this model for short-channel devices at sub 100nm and make a charge conservative model for the parasitic capacitances of FGMOSFET and correspondingly for the transconductances. The enhanced models in future will be added to any circuit simulator that support Verilog-A or Spice syntax.

#### ACKNOWLEDGMENT

The authors thanks Zewail City for Science and Technology and American University in Cairo for being home for their study.

## REFERENCES

- 1. L. S. Miller and J. B. Mullin, "Silicon Processing: CMOS Technology," in *Electronic Materials from Silicon to Organics, New York*, Plenum Press, 1991, ch. 13, sec. 6, pp. 177-179.

- 2. N. Sharma and R. Chandel, "Performance analysis of SRAM cell designed using floating gate MOS," 2017 International Conference on Inventive Communication and Computational Technologies (ICICCT), Coimbatore, 2017, pp. 160-165.

- 3. A. Qassem, R. A. Zewail, Y. Ghallab and Y. Ismail, "A 130 nm CMOS integrated Lab-On-a-Chip based on DeFET sensor for biomedical analysis," *2016 IEEE 59th International Midwest Symposium on Circuits and Systems (MWSCAS)*, Abu Dhabi, 2016, pp. 1-4.

- 4. Sergio Domínguez-Sánchez, Mario Alfredo Reyes-Barranca, Salvador Mendoza-Acevedo, Luis Martín Flores-Nava, "*Analysis and measurement of a photo diode used as a control gate in a floating–gate MOS transistor*," Sensors and Actuators A: Physical, Volume 267, 2017, Pages 210-234, ISSN 0924-4247, <a href="https://doi.org/10.1016/j.sna.2017.09.049">https://doi.org/10.1016/j.sna.2017.09.049</a>.

- 5. A. H. Hassan, Y. Ismail, A. M. Nassar, H. Abd Elhamid, H. S. Ayoub, Y. H. Elbashar, "*Charge independent DC model for floating gate MOSFET*," Microelectronics Journal, unpublished.

- 6. *BSIM3v3 MOSFET Model*, University of California., Berkeley., California, 2005.

- 7. Zina Saheb, "TRANSIT AND DC MODEL OF FLOATING GATE TRANSISTOR IN 90NM CMOS TECHNOLOGY," M.S. thesis, Electrical and Computer Engineering. Dept., Dalhousie. Univ., Halifax, Nova Scotia, 2013.

- 8. BSIM4 MOSFET Model, 4.8.1 ed., University of California., Berkeley., California, 2017, pp. 16.

- 9. Chenming Calvin Hu. (2009, February 13). *Modern Semiconductor Devices for Integrated Circuits*, [online]. Available: <u>https://people.eecs.berkeley.edu/~hu/Chenming-Hu ch6.pdf</u>

- 10. B. Van Zeghbroeck. (2011). *Principles of Semiconductor Devices*. Available: <u>https://ecee.colorado.edu/~bart/book/book/chapter7/ch7\_4.htm</u>