# Influence of annealing temperature on the electrical, structural and surface morphology properties of Au/Cr Schottky contacts on n-type InP

Bhaskar Reddy M, Rajagopal Reddy V

Department of Physics, Government Degree & P.G College, Puttur-517 583, India

bhaskarreddymatli@yahoo.co.in

Department of Physics, Sri Venkateswara University, Tirupati-517 502, India

reddy vrq@rediffmail.com

#### **ABSTRACT**

The influence of rapid thermal annealing on the electrical and structural properties of Au/Cr/n-InP Schottky diode have been investigated by the current-voltage (I-V), capacitance-voltage (C-V), auger electron spectroscopy (AES) and X-ray diffraction (XRD) measurements. The Schottky barrier height (SBH) and ideality factor (n) of the as-deposited Au/Cr/n-InP Schottky diode are 0.51 eV (I-V)/0.64 eV (C-V) and 1.81, respectively. When the contact is annealed at 200 °C in N<sub>2</sub> atmosphere for 1min, a maximum SBH (0.71 eV (I-V)/0.81 eV (C-V)) and low ideality factor (1.15) are achieved for the Au/Cr/n-InP Schottky diode. However, after annealing at 300 °C, the SBH slightly decreases to 0.58 eV (I-V)/0.69 eV (C-V), and ideality factor increases to 1.45, respectively. The SBHs obtained from the Norde and Cheung's methods are closely matched with those obtained from the I-V method. Results show that the optimum annealing temperature for the Au/Cr/n-InP Schottky diode is 200 °C. Further, the discrepancy between SBHs calculated from I-V and C-V methods is also discussed. Moreover, the energy distribution of interface state density is estimated from forward bias I-V characteristics at different annealing temperatures. AES and XRD studies reveal that the formation of indium (In) phases at Au/Cr and InP interface may be the cause for the increase in SBH after annealing at 200 °C. The AFM results show that the overall surface morphology of Au/Cr Schottky contacts is considerably smooth at elevated temperatures.

## Indexing terms/Keywords

n-type InP, Au/Cr Schottky contacts, Barrier heights, Auger electron spectroscopy, X-ray diffraction studies .

## **Academic Discipline And Sub-Disciplines**

Microelectronics, Metal-semiconductor (MS) contacts

#### SUBJECT CLASSIFICATION

Semicondutor Physics, Electrical properties

#### TYPE (METHOD/APPROACH)

Rapid thermal annealing, current-voltage (I-V) and capacitance-voltage (C-V) measurements, Auger electron spectroscopy depth profile, X-ray diffraction measurements, atomic force microscopy.

## Council for Innovative Research

Peer Review Research Publishing System

Journal: JOURNAL OF ADVANCES IN PHYSICS

Vol 5, No.3

japeditor@gmail.com

www.cirjap.com

#### 1.INTRODUCTION

III-V compound semiconductor, especially indium phospide (InP) has received much attention for the fabrication of optoelectronics, microwave devices, integrated circuits used in modern high-speed optical communications and Schottky junctions etc. [1-5]. This is due to direct energy band gap, high electron mobility, radiation hardness and high saturation drift velocity. The Schottky diode is a fundamental component in solid state electronics and has received extensive attention over the few decades. The performance and reliability of Schottky barrier diodes (SBD) strongly depend on the MS interface. Hence it is important to have a full understanding of the reactions of metal contacts with InP. Therefore, the fabrication of high-quality, more reliable Schottky contacts to InP with high barrier height, low-leakage current and good thermal stability is still a challenge. Generally InP Schottky diodes show low barrier height (BH) than desirable due to many reasons. One of them may be the out diffusion of InP atoms into the deposited metal films leaving vacancies or defects within the band gap pinning the Fermi level [6].

Various metal schemes have been used for the formation of Schottky rectifiers on n-InP by many research groups. For example, Cetin et al. [7] prepared Au and Cr/n-InP Schottky barrier diodes and reported that the effective barrier height of the Au and Cr contacts were 0.480 eV, 0.404 eV and 0.524 eV, 0.453 eV from current-voltage (I-V) and capacitancevoltage (C-V) measurements, respectively. Huang et al.[8] studied a high performance of bilayer Pt/Al contacts on n-InP and found to be the effective barrier height of 0.74 eV and ideality factor of 1.11. Reddy et al. [9] investigated the electrical, structural and morphological characteristics of rapidly annealed Pt/Ti double metal structure on n-InP and reported that increase or decrease in Schottky barrier height upon annealing at elevated temperatures could be attributed to the formation of interfacial phases at Pt/Ti interface according to AES and XRD results. Devi et al. [10] investigated the electrical and structural properties of Au/Cu Schottky contacts on n-InP as a function of annealing temperature. They reported that the barrier height increased (0.82 eV (I-V) and 1.04 eV (C-V)) after annealing at 400 °C and decreased (0.75 eV (I-V), 0.88 eV (C-V) upon annealing at 600 °C. Huang and Horng [11] studied the electrical and structural properties of Pt/Al/n-InP Schottky diodes and reported that the double metal contact structure provides better rectification characteristics than single metal/n-lnP Schottky diodes. Reddy et al. [12] investigated the annealing effect on electrical properties and interfacial reactions of Ni/Cu Schottky rectifiers on n-InP. They found that the barrier height decreased with annealing temperature compared to the as-deposited one. Bhaskar Reddy et al. [13] prepared the Au/Ni/n-InP Schottky barrier diode and reported that the barrier heights were effectively influenced by rapid thermal annealing. Naik et al. [14] investgated the electrical and structural properties of Pd/V/n-InP Schottky structure as a function of annealing temperature. They reported that the increase in barrier height after annealing at 200 °C might be due to the formation of indium (In) phases at interface vicinity. Recently, Yatskiv et al. [15] prepared Pt/InP Schottky contact by electrophoretic deposition of Pt nano particles and studied its electrical properties at different temperatures.

Our main objective of this work is to fabricate and characterize the Au/Cr Schottky contacts on n-InP as a function of annealing temperature. As far as we know, no one has investigated the electrical, structural and surface morphological properties of Au/Cr/n-InP Schottky contact at different annealing temperatures. In the present work chromium (Cr) is selected as the first layer since it has low work function as well as to provide the low forward voltage drop. Gold (Au) is used as the second layer in order to prevent oxidation as well as to promote current spreading in the contact and good smoothness to the contact. In this work, we investigate the electrical, structural and morphological properties of Au/Cr Schottky contact on n-type InP at different annealing temperatures. Using various analysis techniques (Forward I-V, C-V, Cheung and Norde methods), the diode parameters such as barrier height ( $\Phi_b$ ), ideality factor (n), series resistance ( $R_s$ ), and interface state density ( $N_{ss}$ ) are calculated and discussed. Also, the interface analysis of Au/Cr/n-InP Schottky diode is investigated by auger electron spectroscopy (AES) depth profile and X-ray diffraction (XRD) measurements at different annealing temperatures.

#### 2.EXPERIMENTAL DETAILS

Liquid Encapsulated Czochralski (LEC) grown undoped n-InP (100) samples with carrier concentration of 5×10<sup>15</sup>cm<sup>-3</sup> were used in the present work. The wafers were initially degreased with organic solutions like trichloroethylene, acetone and methanol by means of ultrasonic agitation for 5 min in each stage to remove the contaminants followed by rinsing in deionised water and then dried in N<sub>2</sub> flow. Further, the samples were etched with HF (49%) and H<sub>2</sub>O (1:10) to remove the native oxides from the wafer surface. Finally, the wafers were rinsed in deionised water. Ohmic contact on back side of the InP wafer was formed by deposition indium (In) metal (500Å) followed by rapid thermal annealing at 350 °C in N2 atmosphere for 1min. The metals Au/Cr (300/200 Å) layers were deposited on the polished side of the InP wafer with a diameter 0.7mm through a stainless- steel mask using a e-beam evaporation system. All evaporations process were carried out under a vacuum pressure of 5×10 6mbar. Sequentially, Schottky contacts were annealed at 100 °C, 200 °C and 300 °C under nitrogen ambient using a rapid thermal annealing (RTA) system. The current-voltage (I-V) and capacitancevoltage (C-V) characteristics of the Au/Cr Schottky contacts to n-InP were measured using a Keithley-source measuring unit (Model No 2400) and automated deep level spectrometer (SIMILAB DLS-83). To examine the intermixture of the Au/Cr metals with InP before and after annealing, auger electron spectroscopy (AES: UG: micro lab 350) depth profile was used. X-ray diffraction studies (Siefert XRD PW 3710) using Cu Kα radiation) were made to characterize the interfacial reaction between the InP and Au/Cr metal layers. Finally, atomic force microscopy (AFM) (Model No: a MOD-1M plus, Make: Nano focus; Operating mode: Non-contact, tip size <10 nm) was also employed to characterize the surface morphology of the Au/Cr Schottky contacts before and after annealing temperature.

### **3.RESULTS AND DISCUSSION**

#### 3.1 The Current-Voltage (I-V) Characteristics

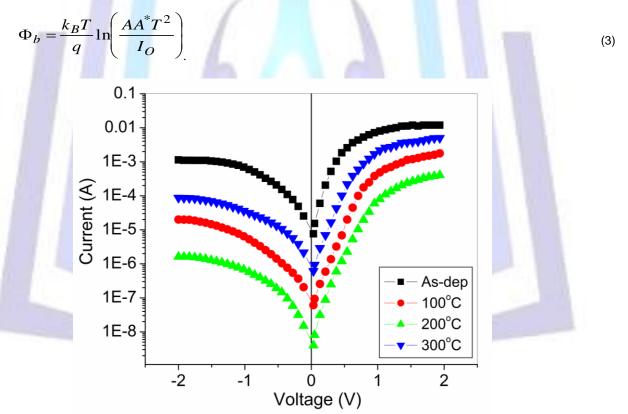

The forward and reverse bias I-V characteristics of Au/Cr/n-InP Schottky diodes are shown in Figure 1 as a function of annealing temperature. The leakage current of the as-deposited and annealed Au/Cr/n-InP Schottky diode at 100 °C are measured to be  $9.961\times10^{-6}$  A and  $8.001\times10^{-8}$  A at -1V. However, for the contact annealed at 200 °C, the leakage current slightly decreases to  $5.373\times10^{-9}$  A at -1V. Further, with the increase in annealing temperature up to 300 °C, the leakage current increases to  $8.079\times10^{-7}$  A at -1V compared to the annealed at 100 °C and 200 °C contacts. Experimental results indicate that the electrical properties of Au/Cr/n-InP Schottky diodes are improved after annealing at 200 °C. According to the thermionic emission (TE) theory, the current through a Schottky barrier diode (SBD) with the series resistance (R<sub>S</sub>) at a forward bias ( $V \ge 3kT/q$ ) and is given by [1]

$$I = I_0 \exp\left(\frac{q(V - IR_S)}{nk_B T}\right) \left[1 - \exp\left(\frac{-q(V - IR_S)}{k_B T}\right)\right]$$

(1)

where I is measured current, V is applied voltage, the term  $IR_s$  is the voltage drop across the  $R_s$  of the diode,  $k_B$  is the Boltzmann's constant, n is ideality factor,  $I_o$  is reverse saturation current derived from the straight line of intercept of In(I) at zero bias and it is given by

$$I_o = AA^*T^2 \exp\left(\frac{-q\Phi_b}{k_BT}\right) \tag{2}$$

where A is the effective area of Schottky contact,  $A^*$  is the effective Richardson constant (the theoretical value of  $A^*$  was 9.4 Acm<sup>-2</sup>K<sup>-2</sup> for n-lnP [16]), q is the charge of electron, T is the absolute temperature and  $\Phi_b$  is the barrier height and is determined from the extrapolated  $I_o$  and is given by

Figure 1.The reverse and forward (I-V) characteristics of the Cr/Au/n-InP Schottky diodes at different temperatures.

The experimental values of Schottky barrier height (SBH) of the as-deposited and 100 °C annealed contacts are found to be 0.51 eV and 0.63 eV respectively. However, the SBH increases to 0.71 eV for the contact annealed at 200 °C. Further, the SBH slightly decreases to 0.58 eV when the contact is annealed at 300 °C. These results indicate that the optimum annealing temperature for the Au/Cr/n-InP Schottky diodes is 200 °C. According to Duboz et al [17], the lower value of the barrier height for the sample annealed at higher temperature can be attributed to reduction in the density of interfacial defects. The modification of the defect density by annealing could change the pinning at the Fermi level resulting change in the barrier heights. The values of ideality factor *n* can be calculated from the slope of the linear region of the forward I-V characteristics for small forward bias currents where the series resistance is negligible. The ideality factor is given by

(7)

$$n = \left(\frac{q}{k_B T}\right) \left(\frac{dV}{d(\ln I)}\right) \tag{4}$$

As it can be seen from Figure 1, at low forward bias voltages, the forward bias I-V characteristics are linear on a semi-log-artimatic scale but deviate considerably from linearity which may be due to the effect of series resistances ( $R_s$ ), the interface layer, and the interface states when the applied voltage is significantly large. The series resistance ( $R_s$ ) is important in the downward curvature of the forward bias I-V characteristics, but the other two Schottky parameters such as barrier height  $\Phi_b$  and ideality factor n are significant in both the linear and non-linear regions of the I-V characteristics. As the linear range of the forward I-V plots is reduced, the accuracy of the determination of SBH and ideality factor becomes smaller. Therefore  $\Phi_b$ , n and  $R_s$  are also estimated from the downward curvature of the forward I-V plot, using Cheung's method [21]. Cheung's functions can be expressed as

$$\frac{dV}{d(\ln I)} = IR_S + n \left( \frac{k_B T}{q} \right)$$

$$H(I) = V - n \left( \frac{k_B T}{q} \right) \ln \left( \frac{I}{AA * T^2} \right)$$

(5)

and H(I) can also be written as  $H(I) = IR_S + n\Phi_b$

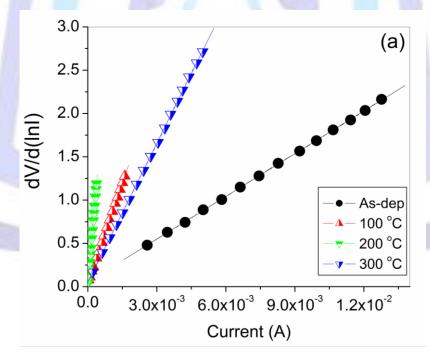

Figure 2. (a) plot of dV/d(InI) versus I for the Cr/Au/n-InP Schottky diode annealed at different temperatures.

Figure 2. (b) plot of H(I) versus I for the Cr/Au/n-InP Schottky diode annealed at different temperatures.

Figure 2(a) and 2(b) show the experimental dV/d(lnI) versus I and H(I) versus I plots for the as-deposited Au/Cr/n-InP Schottky diode and annealed at 100, 200 and 300 °C respectively. The plot of dV/d(lnI) is linear whose slope gives  $R_s$  and the y-axis intercept gives nkT/q from equation (5). The estimated  $R_s$  and n values are 164  $\Omega$  and 2.14 for as-deposited, 768  $\Omega$  and 1.63 for 100 °C, 3022  $\Omega$ , 1.47 for 200 °C and 536  $\Omega$ , 1.86 for 300 °C. The plot of H(I) versus I must be linear according to equation (7) as shown in Figure 2 (b). The slope of H(I) versus I gives a second method to determine the  $R_s$  by using the value of n from equation (6), the  $\Phi_b$  cab be estimated from the y-intercept of H(I) versus I. The determined values of  $R_s$  and  $\Phi_b$  from H(I) versus I plot are 110  $\Omega$ , 667  $\Omega$ , 2692  $\Omega$ , and 465  $\Omega$ , and 0.52 eV, 0.65 eV, 0.71 eV, and 0.58 eV for as-deposited and 100 °C, 200 °C, and 300 °C annealed contacts respectively. These observations revealed that both the  $R_s$  obtained from dV/d(lnI) versus I plot and H(I) versus I are in good agreement with each other, implying their consistency and validity.

In order to determine the effective SBH and series resistance ( $R_s$ ) of Au/Cr/n-InP Schottky diodes, the modified Norde function was also used [22]. In this method a function F(V) is plotted against the V (plot not shown here) and is given by

$$F(V) = \frac{V}{\gamma} - \frac{1}{\beta} \ln \left[ \frac{I(V)}{AA^*T^2} \right]$$

(8)

where  $\gamma$  is the integer (dimensionless) greater than ideality factor n and I(V) is the current obtained from the forward bias I-V curve. The effective SBH ( $\Phi_b$ ) is given by

$$\Phi_b = F(V_{\min}) + \frac{V_{\min}}{2} - \frac{kT}{q} \tag{9}$$

where  $F(V_{min})$  is the minimum point of F(V) and  $V_{min}$  is the corresponding voltage. The value of series resistance  $(R_s)$  is also determined by the norde function and is given by

$$R_s = \frac{k_B T(\gamma - n)}{qI} \tag{10}$$

The extracted SBH and series resistance (R<sub>s</sub>) of the Au/Cr/n-InP Schottky diode are 0.53 eV, 320  $\Omega$  for as-deposited, 0.66 eV,199 k $\Omega$  for 100 °C, 0.73 eV, 272 k $\Omega$  for 200 °C, and 0.60 eV, 15 k $\Omega$  for 300 °C respectively. It is observed that there is a good agreement among the values of  $\Phi_b$  obtained from the forward bias I-V, Cheung's and Norde's methods. Also, series resistance (R<sub>s</sub>) estimated by the Norde's method is comparable to that of the Cheung's method.

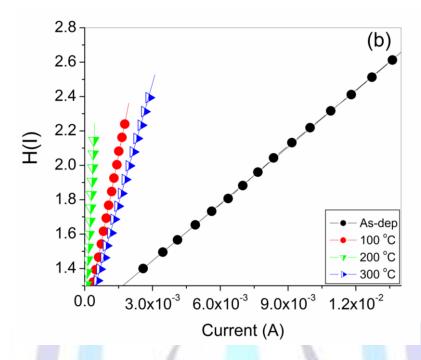

Figure 3. plot of 1/C<sup>2</sup> versus V for the Cr/Au/n-InP Schottky diodes annealed at different temperatures

Capacitance-voltage (C-V) characteristics of the Au/Cr/n-InP Schottky diode are measured at 1MHz in the dark at room temperature. Figure 3 shows a plot of 1/C<sup>2</sup> as a function of bias voltage (V) for the as-deposited and annealed Au/Cr/n-InP Schottky diode. The relationship between the capacitance and the applied voltage in Schottky diodes is given by [1,23]

$$\frac{1}{C^2} = \left(\frac{2}{\varepsilon_S q N_d A^2}\right) \left(V_{bi} - \frac{kT}{q} - V\right) \tag{11}$$

where  $\varepsilon_s$  is the permittivity of the semiconductor ( $\varepsilon_s$ = 9.4  $\varepsilon_o$ , where  $\varepsilon_o$  is the vacuum permittivity) of n-InP, N<sub>d</sub> is the donor concentration, A is the area of the Schottky contact and V<sub>bi</sub> is the flat band voltage respectively. The x-intercept of  $(1/C^2)$  versus V plot yields V<sub>o</sub> and V<sub>o</sub> is related to the built-in potential V<sub>bi</sub> by the equation V<sub>bi</sub> = V<sub>o</sub> + kT/q, where T is the absolute temperature. The barrier height ( $\Phi_o$ ) is given by  $\Phi_o = V_{bi} + V_n$ , where V<sub>n</sub> = (kT/q) ln(N<sub>c</sub>/N<sub>d</sub>). The effective density of states in the conduction band edge is given by N<sub>c</sub> =  $2(2\pi m^*kT/h^2)^{3/2}$ , where m\*= 0.078m<sub>o</sub> and its value is  $5.7 \times 10^{17}$  cm<sup>-3</sup> for InP [24] at room temperature. The SBH of as-deposited Au/Cr/n-InP Schottky diode is found to be 0.64 eV. The estimated SBHs are 0.75 eV for 100 °C, 0.81 eV for 200 °C and 0.69 eV for 300 °C annealed Au/Cr/n-InP Schottky diodes respectively.

Table 1: The electrical parameters of Au/ Cr/n-InP Schottky diode as a function of annealing temperature.

| Sample | Schottky barrier<br>height (Φ <sub>b</sub> ) eV |      | Ideality<br>factor<br>from I-V | Cheung's functions |      |                    |                      | Norde              |                      | Interface                                            |

|--------|-------------------------------------------------|------|--------------------------------|--------------------|------|--------------------|----------------------|--------------------|----------------------|------------------------------------------------------|

|        |                                                 |      |                                | dV/d(InI) vs. I    |      | H(I) vs. I         |                      | Norde              |                      | state density                                        |

|        | I-V                                             | C-V  | n                              | R <sub>s</sub> (Ω) | n    | R <sub>s</sub> (Ω) | (Ф <sub>b</sub> ) eV | R <sub>s</sub> (Ω) | (Ф <sub>b</sub> ) eV | N <sub>ss</sub> (eV <sup>-1</sup> cm <sup>-2</sup> ) |

| As-dep | 0.51                                            | 0.64 | 1.81                           | 164                | 2.14 | 110                | 0.52                 | 320                | 0.53                 | 2.0212x10 <sup>12</sup>                              |

| 100°C  | 0.63                                            | 0.75 | 1.28                           | 768                | 1.63 | 667                | 0.65                 | 199 kΩ             | 0.66                 | 1.0623x10 <sup>12</sup>                              |

| 200°C  | 0.71                                            | 0.81 | 1.15                           | 3022               | 1.47 | 2692               | 0.71                 | 272 kΩ             | 0.73                 | 7.6212x10 <sup>11</sup>                              |

| 300°C  | 0.58                                            | 0.69 | 1.45                           | 536                | 1.86 | 465                | 0.58                 | 15 kΩ              | 0.60                 | 1.4918x10 <sup>12</sup>                              |

A summary of the basic electrical parameters of Au/Cr/n-InP Schottky diodes calculated from I-V and C-V characteristics at different annealing temperature is given in Table 1. As it can be seen from Table 1 that the barrier heights  $(\Phi_{b(I^{-}V)})$  achieved from I-V measurements are significantly lower than those obtained from C-V measurements  $(\Phi_{b(I^{-}V)})$ . Various authors have reported the reasons for the difference in SBHs obtained from I-V and C-V measurements (in the literature) [25-28]. Based on Hacke et al. [25], the presence of a native oxide layer at the metal-semiconductor interface can cause the discrepancy between the measured  $\Phi_{b(I^{-}V)}$  and  $\Phi_{b(C-V)}$ . According to Song et al. [26] the inhomogeneity in the interface layer composition, non-uniformity of the interfacial layer thickness, and distribution of interface charges can also cause such differences in the SBH estimated from I-V and C-V measurements. Further, the surface damage at the metal-

semiconductor interface affects the I-V measurements because defects may act as recombination centers for trap assisted tunneling currents according to Fontaine et al. [27]. One more possibility is that the product of reactions may not be uniform at the interface at a high annealing temperature. The type and reaction phases may vary from one location to another which cause different SBHs [28].

At high current region, there is always a deviation of the ideality factor which may be due to the presence of a interfacial layer between metal and semiconductor, interface states and series resistance. Thus, for estimating SBH and other characteristic parameters, the interface states play an important role in the semiconductor rectifying contacts. It is well known that for a metal/semiconductor diode having interface states in equilibrium with the semiconductor, the ideality factor n becomes greater than unity [29]. The expression of the density of interface states proposed by Card and Rhoderick is given by [29]

$$N_{SS}(V) = \frac{1}{q} \left[ \frac{\varepsilon_i}{\delta} (n(V) - 1) - \frac{\varepsilon_S}{W_D} \right]$$

(12)

where  $\epsilon_{i=3.5}\epsilon_{o}$  and  $\epsilon_{s=9.4}\epsilon_{o}$  are the permittivity of the interfacial layer and semiconductor,  $N_{ss}$  is the interface state density,  $\delta$  is the thickness of the interfacial layer and  $W_{D}$  is the width of the space charge region. Further, in n-InP semiconductor the energy of interface states ( $E_{ss}$ ) with respect to the bottom of the conduction band at the surface of the semiconductor is given by [30,31,32].

$$E_C - E_{SS} = q(\Phi_e - V) \tag{13}$$

where  $E_{ss}$  is the energy corresponding to the bottom of the conduction band at the surface of the semiconductor and  $\Phi_e$  is the effective barrier height, which depends on the applied bias due to an interfacial layer and is given by [33].

$$\Phi_e = \Phi_{bo} + \left(1 - \frac{1}{n}\right)V \tag{14}$$

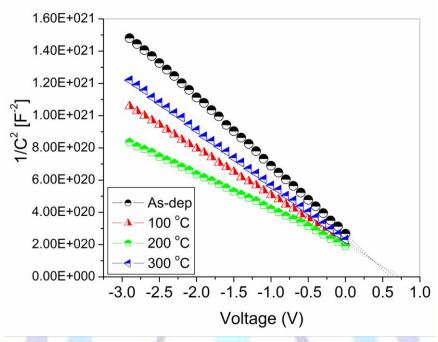

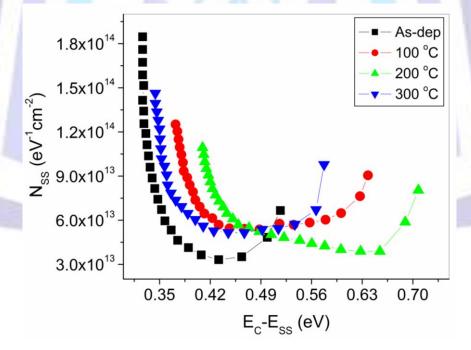

Thus, Eqs. (12)-(14), along with the I-V characteristics can be used for estimation of interface state density ( $N_{ss}$ ) as a function of interface state energy ( $E_{ss}$ ). The  $N_{ss}$  versus  $E_c$ - $E_{ss}$  plot of the Au/Cr/n-InP Schottky diode is shown in Figure 4.

Figure 4. Density of interface states N<sub>ss</sub> as a function of E<sub>c</sub>-E<sub>ss</sub> for the Cr/Au/n-InP Schottky diodes at various temperatures.

It can be seen from Figure 4, an experimental increase in interface state density exists from mid gap towards the bottom of the conduction band is very apparent, and  $N_{ss}$  values obtained decreases with an increase of applied voltages. The value of interface state density is estimated for the as-deposited Au/Cr/n-InP Schottky diode is  $2.021 \times 10^{12} \text{ eV}^{-1} \text{cm}^{-2}$ . For the contacts annealed at 100 °C, 200 °C, and 300 °C, the interface state densities are  $1.062 \times 10^{12} \text{ eV}^{-1} \text{cm}^{-2}$ ,  $7.621 \times 10^{11} \text{ eV}^{-1} \text{cm}^{-2}$ , and  $1.4918 \times 10^{12} \text{ eV}^{-1} \text{cm}^{-2}$  respectively. The results of the alone has explained that the increase in annealing temperature up to 200 °C the values of interface state density are decreased and then slightly increased after annealing at 300 °C. The change in the charge of the interface states and thus the interface state energy distribution due to the

potential drop across the interfacial layer varies with the bias. It alters the diffusion potential and therefore the depletion capacitance [1,24,33]. The expermental results show that the interface states density  $(N_{ss})$ , and series resistance  $(R_s)$  has a significant effect on the electrical characteristics of the Schottky device.

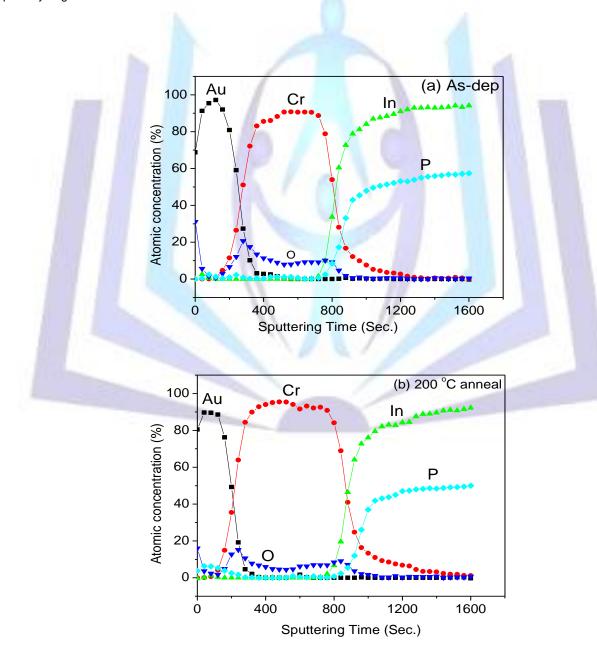

## 3.2 Structural and Morphological Characteristics

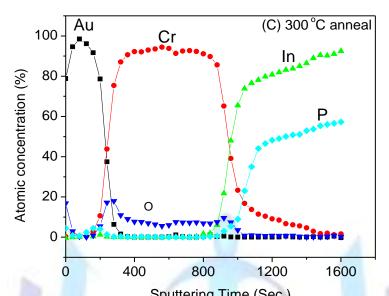

AES depth profile measurement was employed to examine the variation in the BHs of the Au/Cr/n-inP Schottky diode before and after annealing at 300  $^{\circ}$ C in N<sub>2</sub> ambient for 1 min. AES depth profiles of the as-deposited and annealed at 200  $^{\circ}$ C and 300  $^{\circ}$ C are shown in Figure 5. The atomic concentration percentage is recorded as a function of sputtering time to investigate the interfacial reaction between Au/Cr metal layers and InP film. The as-deposited layers Au/Cr, Figure 5(a), exhibit a relative sharp interface indicating that there is no significant inter-diffusion (or) out diffusion between the Au/Cr metal layers and InP layer. When the contact annealed at 200  $^{\circ}$ C, Figure 5(b) AES depth profile of the Au/Cr contact shows that indium (In) is out diffused into Au/Cr film this leads to the possibility of a reaction between Au/Cr and In film, resulting in the formation of Cr-In and Au-In interfacial phases during annealing at 200  $^{\circ}$ C at the interface vicinity. In Figure 5(c), a small change in the interface is observed with further out diffusion of In into Au/Cr layers. It is also noted that a small amount of phosphide (P) is out diffused into metal layers. This indicates the possibility of a P reaction with metal layers. These results lead to formation of phosphide (P) phases at interface during annealing at 300  $^{\circ}$ C as shown in Figure 5(c). Moreover, it is observed that a small amount of oxygen is observed in the interface for all contacts. This may be partially originated from the InP surface.

Sputtering Time (Sec.)

Figure 5. AES depth profiles of Cr/Au/n-InP Schottky diodes: (a) as-deposited, (b) 200 °C annealed and

(c) 300 °C annealed contacts.

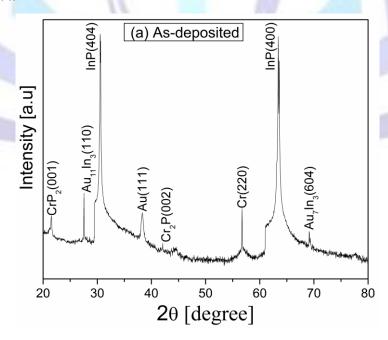

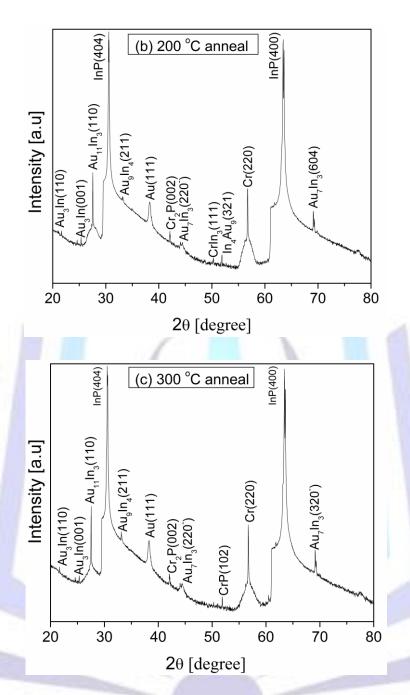

Next, In order to understand the interfacial reactions between deposited metal layers and semiconductor, XRD measurements are performed before and after annealing temperature. Figure 6 shows the XRD spectra of Au/Cr/ n-InP Schottky diodes at different annealing temperatures. For the XRD spectra of the as-deposited contact, Figure 6(a), in addition to the characteristic peaks InP (404), (400) and Au (111), Cr (220) there are some extra peaks which are identified as CrP<sub>2</sub> (001), Au<sub>11</sub>In<sub>3</sub> (110), Cr<sub>2</sub>P (002), Au<sub>7</sub>In<sub>3</sub> (604). For the contact annealed at 200 °C (Figure 6(b)), additional peaks are observed compared to the as-deposited sample. This indicates the formation of new interfacial phases at the interface. These phases are identified as Au<sub>3</sub>In (110), Au<sub>3</sub>In (001), Au<sub>9</sub>In<sub>4</sub> (211), Au<sub>7</sub>In<sub>3</sub> (220), CrIn<sub>3</sub> (111), In<sub>4</sub>Au<sub>9</sub> (321). Figure 6 (c) shows the XRD spectrum of the sample annealed at 300 °C. It is noted that the peaks corresponding to Au<sub>3</sub>In (001), CrIn<sub>3</sub> (111) and In<sub>4</sub>Au<sub>9</sub> (321) observed in the 200 °C annealed sample disappeared in 300 °C annealed sample. Further, a new peak is identified as CrP (102) compared to the as-deposited and 200 °C annealed sample

Figure 6. XRD plots of the Cr/Au/n-InP Schottky diodes: (a) as-deposited, (b) 200 °C annealed and (c) 300 °C annealed samples.

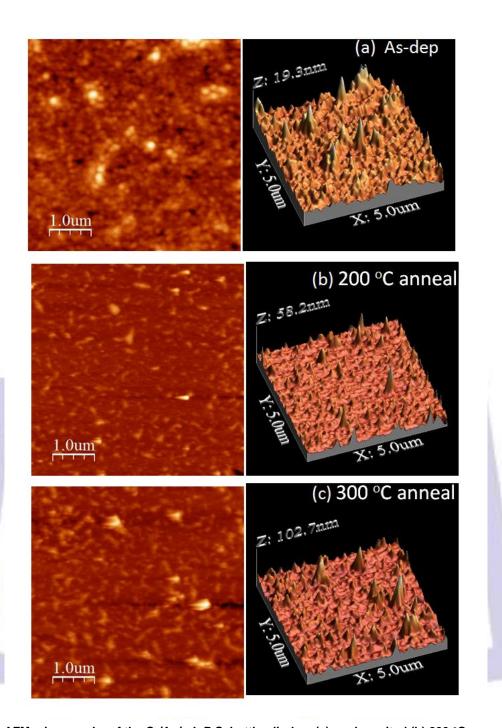

The atomic force microscopy (AFM) is also employed to characterize the surface morphology of the Au/Cr Schottky contacts before and after annealing at 300 °C in  $N_2$  ambient for 1min. Figure 7 shows the AFM images of the as-deposited Au/Cr Schottky contact and annealed at 200 °C and 300 °C. The scanned area of the sample is  $5\times5~\mu m^2$ . The surface morphology of the as-deposited sample is fairly smooth with a root-mean-square (rms) roughness of 1.800 nm as shown in Figure 7(a). When contact is annealed at 200 °C, Figure 7(b), the surface morphology become somewhat degraded with an rms roughness of 3.075 nm. Further, increase in the annealing temperature up to 300 °C, Figure 7(c), it is observed that the surface morphology of the contact is slightly increased with an rms roughness of 7.307 nm as compared to the as-deposited and 200 °C annealed contacts. Results revealed that the Au/Cr Schottky contact has no change in surface degradation significantly even after annealing at 300 °C.

Figure 7. AFM micrographs of the Cr/Au/n-InP Schottky diodes: (a) as-deposited (b) 200 °C annealed and (c) 300 °C annealed samples.

The experimental results exhibit that the barrier height (BH) increases for the contact annealed at 200 °C compared to asdeposited and 100 °C annealed contacts. However, the BH slightly decreases in annealing temperature upto 300 °C. The variation in the BH on annealing may be responsible for the formation of interfacial phases at the interface. The variation in BH of Au/Cr/n-InP Schottky diodes with annealing temperature can be explained based on the AES and XRD results. The XRD and AES depth profile results reveal that, as annealing temperature increases up to 200 °C, an interfacial region formed at the interface, with the out diffusion of indium (In) from the InP into Au/Cr layers as evident from AES and XRD measurements (Figures.6 (b), 5 (b)). As a result, the formation of interfacial phases such as Au<sub>3</sub>In (110) (001), Au<sub>9</sub>In<sub>4</sub> (211), Au<sub>7</sub>In<sub>3</sub> (220), CrIn<sub>3</sub> (111), In<sub>4</sub>Au<sub>9</sub> (321) are responsible for the increase of the BH. The formation of these interfacial phases result in accumulation of fixed negative charge due to the presence of filled acceptors or electrons traps at the InP interface. The increase in the BH is always accompanied by a corresponding decrease in the reverse leakage current. However, the decrease in SBH upon annealing at 300 °C could be attributed the reaction of Cr layer with InP, resulting in the formation of phosphorous (P) phases at the interface vicinity (as evident from Figure 6(c)). The formation of phosphorous phases at interface may create phosphorus vacancies in InP which act as donors, as a result reducing the

SBH at elevated temperature. In this case a positive charge state may exist at the interface due to loss of phosphorous from the surface which may reduce the SBH. These findings are consistent with the results which were previously reported by Andersson [34], Naik et al. [14]. The discrepancy of the BHs of Au/Cr Schottky contacts is mostly due to the observed structural changes of the Au/Cr contacts at the interface.

#### 4.CONCLUSIONS

The electrical, and structural properties of Au/Cr/n-InP Schottky diode have been investigated by I-V, C-V, AES and XRD measurements at different annealing temperatures. The estimated Schottky barrier height (SBH) and ideality factor (n) of the as-deposited Au/Cr/n-InP Schottky diode are 0.51 eV (I-V)/0.64 eV (C-V) and 1.81, respectively. When the contact is annealed at 200 °C in N<sub>2</sub> ambient for 1 min, a maximum SBH and low ideality factor are achieved for Au/Cr/n-InP Schottky diode and the corresponding values are 0.71 eV (I-V)/0.81 eV (C-V) and 1.15. However, the SBH slightly decreases to 0.58 eV (I-V)/0.69 eV (C-V), and ideality factor increases to 1.45 upon annealing at 300 °C. Further, it is noted that the SBHs extracted from the C–V measurements are higher than that obtained from I–V measurements. The SBHs obtained from the Norde and Cheung's methods are closely matched with those obtained from the I-V method. Results show that the optimum annealing temperature for the Au/Cr/n-InP Schottky diode is 200 °C. It is noted that the extracted interface state density N<sub>ss</sub> decreases with an increase in annealing up to 200 °C and then slightly increases upon annealing at 300 °C. Based on the AES and XRD results, the formation of indium phases at the interface may be the reason for the increase of SBHs after annealing at 200 °C. The decrease in SBH for contact annealed at 300 °C may be the reason for the formation of phosphide phases at the interface. The AFM results show that the surface morphology of the as-deposited Au/Cr Schottky contacts (rms roughness of 1.800 nm) is increased for the contact annealed at 300 °C (rms roughness of 7.307 nm). Expermental results indicate that the Au/Cr Schottky contact may be good choice for the development of InP-based electronic device applications.

### **5.ACKNOWLEDGMENTS**

The authors thank the University Grant Commission (UGC-SERO), Hyderabad for providing the financial assistance (No: F. MRP-4247/12 UGC-SERO dated: March, 2013).

#### **6.REFERENCES**

- [1] Rhoderick, E. H. and Williams, R. H. 1988. Metal-Semiconductor Contacts. Clarandon Press. Oxford.

- [2] Williams, R. H. and Robinson, G. Y. 1985. In Physics and Chemistry of III–V Compound Semiconductor Interfaces, Ed. By C. W. Wilmsen. Plenum Press.New York.

- [3] Cetin, H., Ayyildiz, E., and Turut, A. 2005. Barrier Height Enhancement And Stability Of The Au/N-Inp Schottky Barrier Diodes Oxidized By Absorbed Water Vapour", J Vac Sci Technol B J. Vac. Sci. Technol. B. 23, 2436-2443.

- [4] Oztas, M., Bedir, M., Kayalı, R., and Aksoy, F. 2006. Influence of the annealing conditions on the properties of InP thin films. Mater. Sci. Eng. B 131, 94-99.

- [5] Van Meirhaeghe, R. L., Lafle're, W. H., and Cardon, F. 1994. Influence of defect passivation by hydrogen on the Schottky barrier height of GaAs and InP contacts. J. Appl. Phys. 76, 403-406.

- [6] Spicer, W. E., Lindau, I., Skeath, P., Su, C.Y., and Chye P. 1980. Unified Mechanism for Schottky-Barrier Formation and III-V Oxide Interface States. Phys. Rev. Lett. 44, 420-423.

- [7] Cetin, H. and Ayyildiz E. 2010. On Barrier Height Inhomogeneities Of Au And Cu/N-Inp Schottky Contacts. Physica B 405, 559-563.

- [8] Huang, W. –C. and Cai, D. –R. 2006. Formation and characterization of aluminum-oxide by stack-layered metal structure Schottky diode In: International Workshop on Junction Technology. 295-298.

- [9] Rajagopal Reddy, V., Subba Reddy, D., Sankar Naik, S., and Choi, C. -J. 2011. Structural, electrical, and surface morphological characteristics of rapidly annealed Pt/Ti Schottky contacts to n-type InP. Phys. Status Solidi A. 208, 2406-14.

- [10] Lakshmi Devi, V., Jyothi, I., Rajagopal Reddy, V., and Choi, C. –J. 2012. Schottky barrier parameters and interfacial reactions of rapidly annealed Au/Cu bilayer metal scheme on n-type InP. The Open Applied Phys. Journal 5, 1-9.

- [11] Huang W. C. and Horng, C. -T. 2011. Electrical and structural properties of a stacked metal layer contact to n-InP Appl. Surf. Sci. 257, 3565-3569.

- [12] Munikrishna Reddy, Y., Nagaraj, M. K., Sankar Naik, S., and Rajagopal Reddy, V. 2012. Annealing effects on electrical properties and interfacial reactions of Ni/Cu Schottky rectifiers on n-type InP. J. Modern Phys. 3, 538-545.

- [13] Bhaskar Reddy, M., Janardhanam, V., Ashok Kumar, A., Rajagopal Reddy V., and Narasimha Reddy, P. 2010. Influence of rapid thermal annealing on electrical and structural properties of double metal structure Au/Ni/n-InP (111) diodes. Curr. Appl. Phys. 10, 687-692.

- [14] Sankar Naik, S., Rajagopal Reddy, V., Choi, C.-J., and Bae J. -S., 2012. Electrical and structural Properties of Pd/V/n-Type InP Schottky structure as a function of annealing Temperature. Surf. And Interface Analy. 44, 98-104.

- [15] Yatskiv, R., Grym, J., Brus, V.V., Cernohorsky, O., Maryanchuk, P. D., Bazioti, C., Dimitrakopulos, G. P. and Komninou, Ph. 2014. Transport properties of metal–semiconductor junctions on n-type InP prepared by electrophoretic deposition of Pt nanoparticles. Semicond. Sci. and Technol. 29, 045017 (1-8).

- [16] Quan, D. T. and Hbib, H. 1993. High barrier height Au/n-type InP Schottky contacts with a POxNyHz interfacial layer Solid State Electron. 36, 339-344.

- [17] Duboz, J. Y., Binet, F., Laurent, N., Rosencher, E., Scholz, F., Harle, V., Briot, O., Gil, B., and Aulombard, R. L. 1996. Influence of surface defects on the characteristics of GaN Schottky diodes. Material Research Society Symposium Proceedings. 449, 1085-1090.

- [18] Klein, A., Sauberlich, F., Spath, B., Schulmeyer, T., and Kraft, D. 2007. Non-stoichiometry and electronic properties of interfaces. J. Mater. Sci. 42, 1890-900.

- [19] Werner, J. H. and Guttler, H. H. 1991. Barrier inhomogeneities at Schottky contacts. J. Appl. Phys. 69, 1522–33.

- [20] Hudait, M. K., and Krupanidhi, S. B. 2001. Interface states density distribution in Au/n-GaAs Schottky diodes on n-GaAs substrates. Mat. Sci. Eng. B 87, 141-147.

- [21] Cheung, S. K. and Cheung, N. W. 1986. Extraction of Schottky diode parameters from forward current-voltage characteristics. Appl. Phys. Lett. 49, 85-87.

- [22] Norde, H. 1979. A modified forward I-V Plot for Schottky diodes with high series resistance. J. Appl. Phys. 50, 5052-5053.

- [23] Sze, S. M. 1981. Physics of Semiconductor Devices. Willey. New York.

- [24] Wilmsen, C. W. 1985. Physics and Chemistry of III–V Compound Semiconductor Interfaces. Plenum Press. New York.

- [25] Hacke, P., Detchprohm, T., Hiramatsu, K., and Sawaki, N. 1993. Schottky barrier on *n*-type GaN grown by hydride vapor phase epitaxy. Appl. Phys. Lett. 63, 2676.

- [26] Song, Y. P., Van Meirhaeghe, R.L., Laflere, W. H., and Cardon, F. 1986. On the difference in apparent barrier height as obtained from capacitance-voltage and current-voltage-temperature measurements on Al/p-InP Schottky barriers. Solid State Electron. 29, 633-638.

- [27] Fontaine, C., Okumura, T., and Tu, K. N. 1983. Interfacial reactions and Schottky barriers between Pt and GaAs. J. Appl. Phys. 54, 1404-1412.

- [28] Dasaradha Rao, L., Rajagopal Reddy, V., Janardhanam, V., Kang, M. –S., Son, B. –C., Choi, C. –J. 2014. Electrical and structural properties of rapidly annealed rare-earth metal Er Schottky contacts on p-type InP. Superlattices Microstruct. 65, 206-218.

- [29] Card, H. C. and Rhoderick, E. H. 1971. Studies of tunnel MOS diodes I. Interface effects in silicon Schottky diodes. J. Phys. D; Appl. Phys. 4, 1589-1601.

- [30] Karatas, S., Altindal, S., and Cakar, M. 2005. Current transport in Zn/p-Si(1 0 0) Schottky barrier diodes at high temperatures Physica B 357, 386–397.

- [31] Karatas, S., Altindal, S., Turut, A., and Ozmen, A. 2003. Temperature dependence of characteristic parameters of the H-terminated Sn/p-Si(1 0 0) Schottky contacts. Appl. Surf. Sci. 217, 250-260.

- [32] Turut, A., Saglam, M., Efeoglu, H., Yalcin, N., Yildirim, M., and Abay, B. 1995. Interpreting the nonideal reverse bias C-V characteristics and importance of the dependence of Schottky barrier height on applied voltage Physica B, 205, 41–50.

- [33] Karatas, S. and Turut, A. 2006. The determination of electronic and interface state density distributions of Au/n-type GaAs Schottky barrier diodes. Physica B 381, 199–203.

- [34] Andersson, M. 1993. Ternary phase equilibria in the (Cr, Mo, W)/InP systems at 600°C. J. Alloy. And Compo., 198, L15-L18

## Author' biography with Photo

Dr. M.Bhaskar Reddy did his M.Sc and M.Phil degrees in Physics from Sri Venkateswara University, Tirupati in 1986 and 1988 and was awarded Ph.D in Physics in the same university in 2009. Dr Reddy has published more than 7 articles in referred journals, and has been author/co-author of over 15 National / International conference papers. His current research interests are ohmic and Schottky contacts to III-V and II-VI compound semiconductors. He completed one UGC-SERO Minor Research Project and has one ongoing Minor Research Project. Dr Reddy was conferred with State Best Teacher Award 2013 by the Government of Andhra Pradesh for his contribution in the field of Teaching, Research& Consultancy and Extension& Support activities. He has also been acting as Coordinator for Internal Quality Assurance Cell (IQAC).

Prof.V.Rajagopal Reddy received the M.Sc and Ph.D degrees in Physics from Sri Venkateswara University, Tirupati in 1989 and 1994. From September 2002 to December 2003, Prof. Reddy was a Visiting Research Professor, at the Semiconductor Thin Film and Device laboratory, Gwanju Institute of Science and Technology, Gwanju, Korea, where he performed research on Ohmic and Schottky Contacts to wide band gap semiconductors (GaN). Prof. Reddy has published more than 125 articles in referred journals, and has been author or co-author of over 75 conference papers. Prof. Reddy has successfully guided 12 Ph.Ds in the field of Advanced Electronic Materials (GaN). His current research interests are (i) Ohmic and Schottky Contacts to wide-band gap semiconductors, (ii) Polymer-based Schottky Contacts to InP, (iii) Surface analysis of III-V and II-VI semiconductors, and (iv) Deep level studies in wide band gap semiconductors such as GaN, ZnO.