# Bridgeless SEPIC Converter Based Computer Power Supply Using Coupled Inductor

Dr. Karpagavalli P, Sathiya M

Assistant professor, Department of Electrical and Electronics, Government college of Engineering, Salem, India. pkarpagavalli@vahoo.co.in

PG scholar, Department of Electrical and Electronics, Government college of Engineering, Salem, India. manisathiya68@gmail.com

### **ABSTRACT**

Switched Mode Power Supplies (SMPS) are used as power source for computers. Conventional SMPS used in computers are suffered by some serious problems such as poor power quality, high device stress, slow dynamic response, high harmonic contents, periodically dense, peak currents, distorted input current. To minimize these problems, a non-isolated bridgeless buck-boost single ended primary inductance converter (SEPIC) using coupled inductor is introduced at the front end of the SMPS, which is operated in discontinuous conduction mode (DCM). This proposed technique reduces the Total Harmonic Distortion(THD), which results in power factor improvement. The DC output voltage of the SMPS is almost a constant voltage which is regulated by means of the proposed SEPIC converter. For obtaining different dc voltage levels for the PC applications, the output of the front end SEPIC converter is fed to the half-bridge DC-DC converter. The output voltages of the SMPS are controlled by controlling any one of the output voltages. Design and simulation of the proposed converter are carried out using the MATLAB/simulink software.

## **Keywords**

Bridgeless converters; PFC; computer power supply; power quality; total harmonic distortion

## **Academic Discipline And Sub-Disciplines**

Electrical and Electronics engineering; Power electronics and drives

#### INTRODUCTION

The classical method of ac-dc rectification having a diode bridge rectifier (DBR) followed by the large electrolytic capacitor is used in many electronic applications. The harmonic rich current drawn from the utility due to the uncontrolled charging and discharging of the capacitor goes against the international power quality standards [4-5]. The most commonly affected electronic equipment by the power quality problem is the personal computer (PC). To maintain the harmonics within the limits and also to obtain regulated multiple outputs single stage and two stage conversions of ac voltage into dc voltage have been used in computers. However the single stage power conversion is simple, cost-effective and compact, it suffers from poor dynamic response, complexity in control, large value of capacitance and the component stress is high. So, we go for two stage conversion of ac voltage into multiple dc voltage in computers [6]. Compared to the single stage conversion the number of components used in two stage is much higher. But ,it has fast dynamic response ,provides better regulation in output voltage and blocks the second harmonics(100Hz or 120 Hz) in the first stage itself , so the use of large capacitors are avoided.

For providing PFC in power supplies a boost converter is mostly used. As the input voltage range required is large it is not preferred. For an input supply of 220V, the boost converter cannot control the voltage less than 300V. So, in PCs where wide variations in input voltage and load are expected a buck-boost converter is preferred [7-8]. As the computer power supply is connected to various ICs low output voltage ripple is preferred. Single stage power supplies where power quality improvement and voltage regulation takes place in a single stage are used in many applications. However, in computers, at varying loads the single stage conversion increases the switching stress and reduces the voltage regulation. Hence, to improve the input power quality and regulation in output voltage, we go for two stage conversion. But, the efficiency of the conventional SMPS is higher than the two stage SMPS [9]. To overcome this disadvantage, a new bridgeless front end converter for computer power supplies is proposed. A bridgeless SEPIC converter using coupled inductor is used as the front end converter. A key advantage of using coupled inductor is that the regulator's ripple current is divided between the coupled inductors allowing the value to be halved. The inductive reactance is also reduced which leads to low power dissipation in the form of heat. This design leads to the smaller input capacitor and simple EMI filter. Also, the coupled inductor design provides better feedback control than the uncoupled inductors. A half bridge converter providing isolation, regulation and multiple dc outputs [10-11] is connected at the output of the front end converter.

Previously, a power quality improved bridgeless converter based computer power supply was proposed which uses single inductors having high THD value and low power factor. In this paper, we have proposed a new design which employs coupled inductor instead of single inductors in bridgeless SEPIC converter, operating in discontinuous conduction mode (DCM) which results in the cancellation of current ripple[12] is used at the front end of the SMPS. This reduces the Total Harmonic Distortion and improves the power factor of the converter. The isolated converter is connected to the output of the bridgeless PFC converter. The simulated performance of the proposed multiple-output SMPS with reduced harmonics and improved power quality is provided in the test results.

#### SYSTEM CONFIGURATION

The proposed technique consists of two parts, bridgeless front end ac-dc converter and multi-output isolated dc-dc converter. Based on the requirement of the user the continuous conduction mode (CCM) or the discontinuous conduction mode (DCM) of the bridgeless front end converter is selected. If cost is the major consideration, DCM is selected; if not CCM is preferred. CCM reduces the device stress, but it requires two voltage and one current sensor which makes it costlier. Therefore, a DCM operation where only one voltage sensor is needed for both sensing and control, is preferred at the front end PFC converter. Hence, for achieving inherent PFC the front end converter is designed in DCM, whereas CCM for the isolated converter. For both converters the control loops are independent of each other. The system configuration of the SMPS is described below.

## **Bridgeless Sepic Converter Using Coupled Inductor**

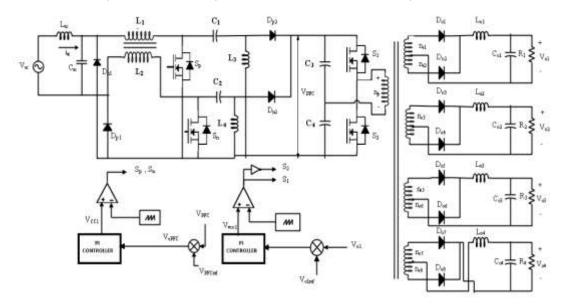

The design of the proposed power supply is shown in the Fig 1. In this proposed technique coupled inductors are used instead of the single inductors at the input side of the Power Factor Correction (PFC) converter. By using two SEPICs at the input side ,Diode Bridge Rectifier (DBR) is eliminated. The SEPIC converters designed with the coupled inductors are free from leakage inductance, in which the AC current losses are reduced. For positive half cycle, the upper converter operates and the lower converter operates for the negative half cycle of the input ac voltage. For the efficient control of both the converters the switching frequency is set to 20KHz. For reducing the complexity in control, the design of the output inductors is carried out in DCM for both the converters. The wide variations in the input voltage and the load is taken care by the regulation of the output voltage. The voltage error (V<sub>ePFC</sub>) is obtained by comparing the output dc voltage (V<sub>epfC</sub>) and the reference voltage (V<sub>epfCref</sub>) which is given to the proportional and the integral controller.

Fig 1:Schematic diagram of bridgeless converter using coupled inductor

To generate the PWM pulses that are given to both the switches the PI controller output ( $V_{cc1}$ ) is compared with a high frequency saw-tooth 1 wave. If  $S_1 < V_{cc1}$  and  $V_{ac}$  is positive, then  $S_p$  is turned on, or else it stays off. The switching signals for the bridgeless ac-dc converter is represented by  $S_t$ . According to the output of the PI voltage controller-1 the width of the PWM pulses vary, so that the dc output voltage  $V_{PFC}$  is effectively regulated, and to obtain the multiple isolated regulated voltage at the output, it is fed to the isolated half bridge converter in the second stage. To maintain the dc output voltage  $V_{PFC}$  constant, the width of the PWM pulses changes accordingly. The multi-winding high frequency transformer (HFC) is used for isolation. To reduce the conduction losses a centre tapped configuration is chosen at the output side. One control loop is used to control all the secondary windings. For the selection of voltage sensing, the highest rated secondary winding is used. The PI controller-2 is fed by the difference between the output voltage ( $V_{01}$ ) and the reference voltage ( $V_{01}$ ref) and its output is compared with another high frequency saw-tooth wave-2, which generates the second set of PWM pulses for the half-bridge converter switches  $S_1$  and  $S_2$ . To avoid the shoot-through fault care should be taken to provide sufficient dead-time between turning OFF of  $S_1$  and turning ON of  $S_2$ . The stress will be reduced if the isolated converter is operated in CCM. The duty cycle changes accordingly, if the load changes in any of the winding, to provide the regulated output dc voltage. The response is slower for the other outputs then the one whose voltage is sensed.

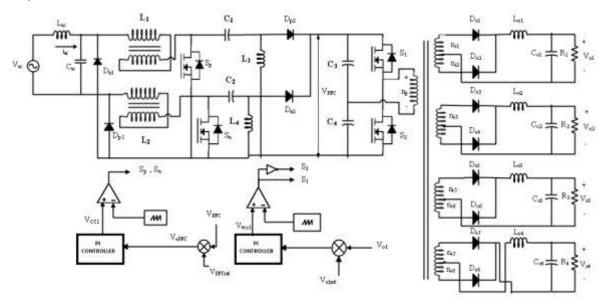

### **Bridgeless Sepic Converter Using Two Coupled Inductor**

The configuration of the modified bridgeless SEPIC converter is same as the proposed technique in which the two input single inductors are replaced by the coupled inductor is shown in fig 2. Here the coupled inductors are in the form of series connection. If the coupled inductors are used, the ripple current is divided between the inductors, so the inductance value required is halved. So, the design of the EMI filter is simple and the

Journal of Advances in chemistry

input capacitor is small. This modified configuration will leads to further reduction in Total Harmonic Distortion (THD).

Fig 2: Schematic diagram of bridgeless converter using two coupled inductors

## **OPERATING PRINCIPLE**

The operating principle of the front end converter and the isolated converters are described below.

# **Operating Principle Of Front End Converter**

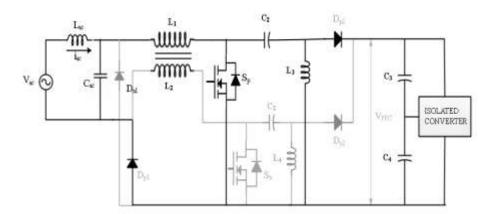

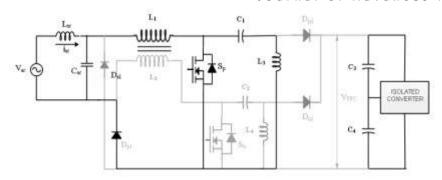

The upper SEPIC converter operates during the positive half cycle of the input voltage as shown in the Fig.3. In the same way, the lower SEPIC operates during the negative half way. The operation of the converter for PWM cycle is described in the following modes.

Fig 3: Operation of PFC converter when input voltage is positive

In the first mode, when Sp turns on, the inductor Lp1 starts storing energy, transferred from the ac mains as shown in the Fig 4. The current path is completed by the diode D<sub>p1</sub>.

Fig 4: Operation of PFC converter during mode I

In the second mode, S<sub>P</sub> is turned off and the diode D<sub>p2</sub> starts conducting. The output inductor L<sub>p2</sub> starts discharging to zero as shown in Fig 5

Fig 5: Operation of PFC converter during mode II

Until the next switching cycle, the current in the inductor remains zero. This mode makes sure the DCM operation as shown in the Fig 6.

Fig 6: Operation of PFC converter during mode III

### Operating Principle of the Isolated Converter

In one switching cycle two high frequency switches are turned on and off. So, the operation of the converter is same in both the half cycles. The switch S<sub>1</sub> is turned on during the first half cycle. On the secondary side, diodes (D<sub>01</sub>, D<sub>03</sub>, D<sub>05</sub> and D<sub>07</sub>) starts conducting and the energy gets stored in the inductors (L<sub>01</sub>-L<sub>04</sub>) in all the secondary winding. When the maximum value is reached by the inductor current, the switch S<sub>1</sub> is turned off. To maintain the constant output dc voltage, all the capacitors in the filters discharge through the load. The upper switch is turned off for the next half cycle. The inductor currents are free-wheeled through the secondary diodes (D<sub>01</sub>-D<sub>08</sub>). The net voltage across the HFT becomes zero, as the core flux is cancelled by the current in all secondary windings. In the next half cycle, the same inductor gets charged and discharged with the lower switches S2. The operating principle of the front end converter and the isolated converter is same for both the proposed bridgeless SEPIC converter using coupled inductor.

## DESIGN OF THE PROPOSED BRIDGELESS SEPIC CONVERTER BASED COMPUTER **POWER SUPPLY**

The design of the proposed bridgeless SEPIC converter using coupled inductor is described below:

#### **Design Of The Proposed Smps System**

The design for both positive and negative half cycle operated PFC is same. The average voltage V<sub>avg</sub> is calculated as,

$$V_{avg} = \frac{2\sqrt{2}V_{ac}}{\pi} = \frac{2\sqrt{2} \times 220V}{3.14} = 198V \tag{1}$$

The duty cycle D of the PFC SEPIC converter is expressed as the ratio of output dc voltage to the sum of output voltage and the input voltage.  $D = \frac{V_{PFC}}{V_{PFC} + V_{avg}} = \frac{300 \, V}{300 V + 198 V} = 0.6 \tag{2}$

$$D = \frac{V_{PFC}}{V_{PFC} + V_{ava}} = \frac{300V}{300V + 198V} = 0.6$$

(2)

Irrespective of the input voltage variation ,the output voltage is maintained constant at 300V. The duty cycle for the supply voltages are calculated as,  $D_{170}$ =0.63,  $D_{220}$ =0.58,  $D_{270}$ =0.52. During the DCM operation, the duty cycle of the converter is considered less than D<sub>270</sub> for the efficient control.

The input inductor value is calculated for the ripple in 40% of input current.

Assume D=0.25

$$L_1 = \frac{DV_{avg}}{f \times (i_{rippls})} = \frac{0.25 \times 198V}{20KHz \times 0.58A} = 4.35mH$$

(3)

Where, f is the frequency.

To make sure the DCM operation, in all operating conditions the output inductor is selected as 100µH.

The capacitor value is calculated as,

$$C_1 = \frac{1}{\omega_r (L_1 + L_2)} = \frac{1}{2 \times \pi \times 20000 Hz (4.35 mH + 100 \mu H)} = 1.78 mF \tag{4}$$

Where,  $\omega_r$  is the angular frequency ( $\omega_r = 2\pi f_r$ ).

To reduce the higher order harmonics an L-C filter is used at the input side [22].

The calculation for the inductance of the secondary winding is,

$$L_{01} = \frac{V_{01}(0.5 - D_s)}{f_s \Delta i_{L01}} = \frac{12V(0.5 - 0.4)}{60KHz \times 0.625A} = 0.032mH \tag{5}$$

Similarly, the inductances for the other secondary windings are 9.5µH, 6.8µH, and 1.5µH.

# SIMULATION CIRCUIT OF BRIDGELESS SEPIC CONVERTER USING COUPLED **INDUCTOR**

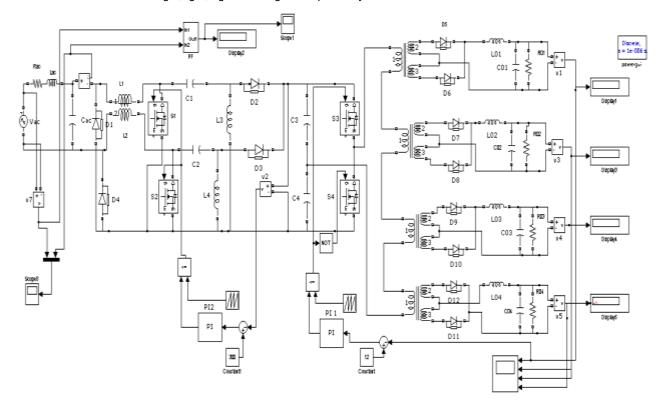

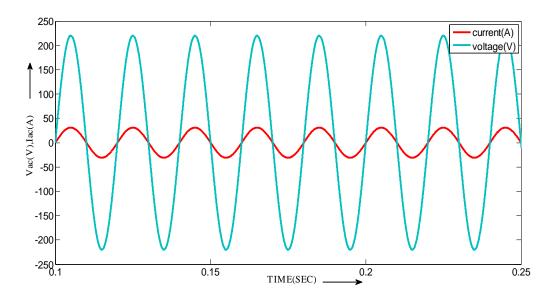

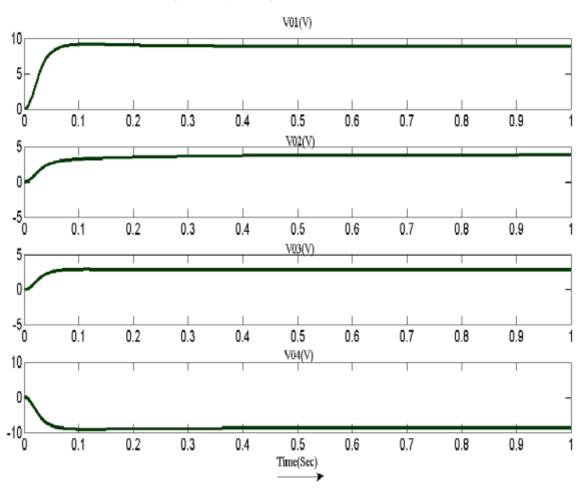

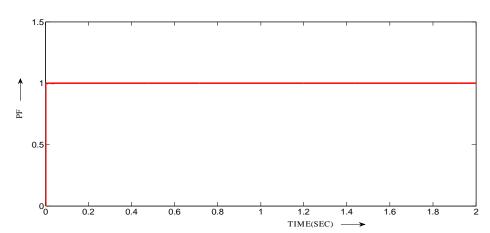

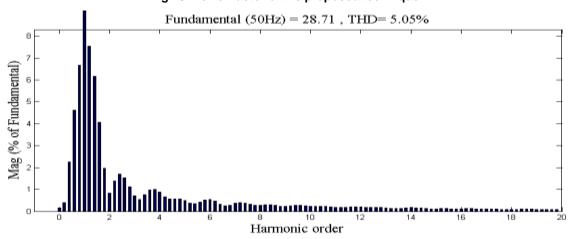

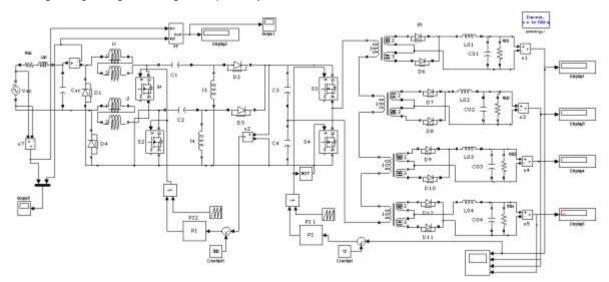

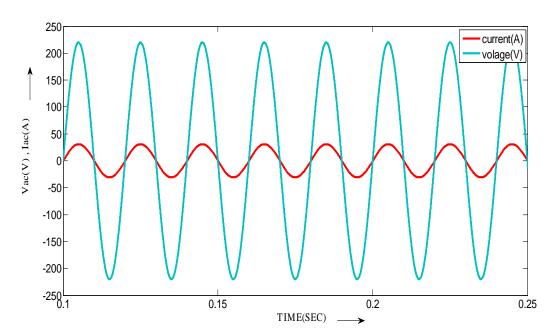

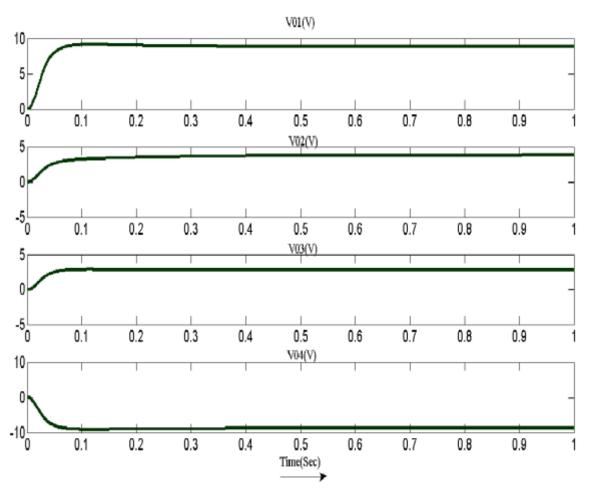

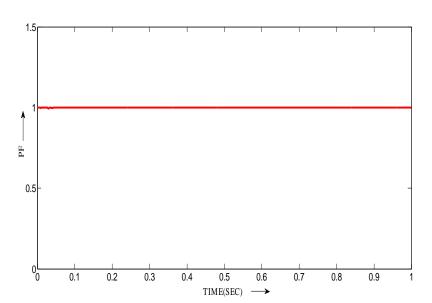

The simulation circuit of the bridgeless SEPIC converter using coupled inductor is shown in the fig 7. The simulated performance for both the proposed techniques are carried out using the MATLAB/SIMULINK software. The response of the simulation are shown in fig 8,fig 9, fig 10 and fig 11 respectively.

Fig 7: Simulation of bridgeless SEPIC converter using coupled inductor.

Fig 8: Supply voltage and current waveform

Fig 9: Output voltage waveform

Fig 10: Power factor of the proposed technique

Fig 11: THD of the proposed technique

# Simulation Circuit Of Bridgeless Sepic Converter Using Two Coupled Inductor

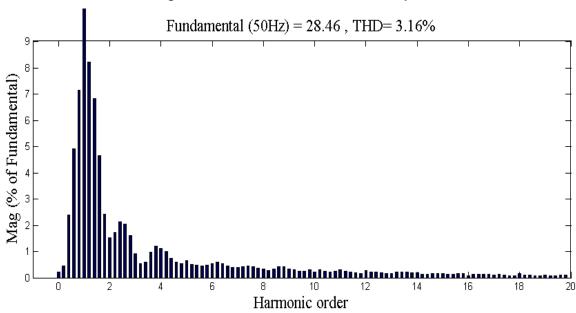

The simulation circuit of the bridgeless SEPIC converter using two coupled inductor is shown in the fig 12 and its response is shown in fig 13, fig 14, fig 15 and fig 16 respectively.

Fig 12: Simulation circuit of the bridgeless SEPIC converter using two coupled inductors

December 2016

Fig 13: Supply voltage and current waveform

Fig 14: Output voltage waveform

Fig 15: Power factor of the modified technique

Fig 16: THD of the modified circuit

# **RESULT**

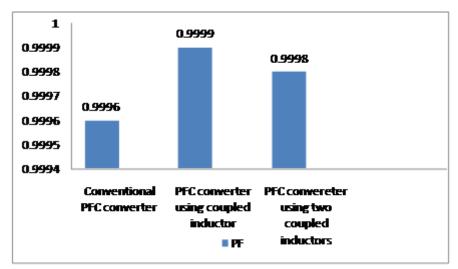

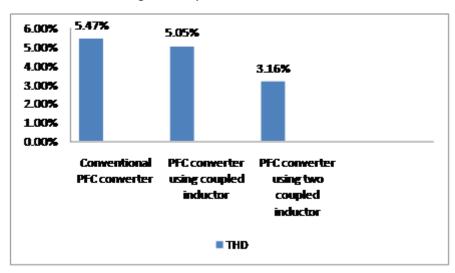

The performance of the proposed systems are computed and the results are compared as shown in the table I. Fig 17 and fig 18 shows the variation of power factor and THD.

Table 1. Performance comparison of different SEPIC converter topologies

| S.no | Techniques                               | Power factor | Thd   |

|------|------------------------------------------|--------------|-------|

| 1.   | Conventional PFC<br>Converter            | 0.9996       | 5.47% |

| 2.   | PFC Converter using coupled inductor     | 0.9999       | 5.05% |

| 3.   | PFC converter using two coupled inductor | 0.9998       | 3.16% |

Fig 17: Comparison of Power factor

Fig 18: Comparison of THD

From the results obtained, we observe that the performance of the bridgeless SEPIC converter using coupled inductor is better than the conventional type SMPS. The power factor the PFC converter is increased to 0.9998 from 0.9996 and the THD is decreased from 5.47% to 3.16%. So, the bridgeless SEPIC converter using couple inductor proves to be the best solution for the power quality problems in the computer applications.

### CONCLUSION

The power quality problems present in the conventional computer power supply is reduced by proposing a bridgeless non-isolated SEPIC converter using coupled inductor. Under the wide variations of input voltages and the loads the proposed power supply will operate efficiently. The proposed technique results in improved power factor from 0.9996 to 0.9998 and reduction in Total Harmonic Distortion from 5.47% to 3.16% when compared to the conventional power supply. They also confirm the fact that power quality problems at the front end are reduced and are recommended solutions for the power quality problems arising in the computers and other similar applications.

#### REFERENCES

- S. Singh, B. Singh, G. Bhuvaneswari and V. Bist, "A Power Quality Improved Bridgeless Converter-Based Computer Power Supply," in IEEE Transactions on Industry Applications, vol. 52, no. 5, pp. 4385-4394, Sept.-Oct. 2016.

- 2. K. Mino, H. Matsumoto, Y. Nemoto, S. Fujita, D. Kawasaki, Ryuji Yamada, and N. Tawada, 2010, "A front-end converter with high reliability and high efficiency," in IEEE Conf. on Energy Conversion Congress and Exposition (ECCE), pp. 3216-3223.

December 2016

- - Jih-Sheng Lai and D. Chen, 1993, "Design consideration for power factor correction boost converter operating at the boundary of continuous conduction mode and discontinuous conduction mode," in Eighth Annual Conf. on Applied Power Electronics Conference and Exposition, APEC'93, pp. 267-273.

- 4. D. O. Koval and C. Carter, May/June1997, "Power quality characteristics of computer loads," IEEE Trans. on Industry Applications, vol. 33, no. 3, pp. 613-621.

- Abraham I. Pressman, Keith Billings and Taylor Morey, 2009, "Switching Power Supply Design," 3rd ed., McGraw Hill. New York.

- 6. C. A. Gallo, F. L. Tofoli and J. A. C. Pinto, Nov. 2010, "Two-stage isolated switch-mode power supply with high efficiency and high input power factor," IEEE Trans. Ind. Elect., vol. 57, no. 11, pp. 3754-3766.

- 7. Fernandez, J. Sebastian, M. M. Hernando, J. A. Martin-Ramos and J. Corral, 2005, "Multiple output AC/DC converter with an internal DC UPS," IEEE Trans. Industrial Electronics, vol. 53, no. 1, pp. 296-304.

- S. N. Padhy and S. Kalra, 2013, "A high performance bridgeless AC-DC-DC power factor corrector for LED driver application," in Annual IEEE Conf. on India Conference (INDICON), pp. 1-6.

- Shikha Singh, Bhim Singh, G. Bhuvaneswari and Vashist Bist, Sept. 2015, "Power factor corrected zeta converter based improved power quality switched mode power supply," IEEE Trans. on Industrial Electronics, vol.62, no. 9, pp.5422-5433.

- 10. Arias, . Fernandez Diaz, D. G. Lamar, D. Balocco, A. A. Diallo and . Sebastin, May 2013, "High-efficiency asymmetrical half-bridge converter without electrolytic capacitor for low-output-voltage ac-dc led drivers," IEEE Trans. Power Elect., vol. 28, no. 5, pp. 2539-2550.

- 11. A. . Perin and I. Barbi, 1992, "A new isolated half-bridge soft-switching pulse-width modulated DC-DC converter," in Seventh Annual IEEE Conf. on Applied Power Electronics Conference and Exposition, APEC'92, pp. 66-72

- 12. Jieli Li, Charles R. Sullivan, Aaron Schultz, APEC 2002, "Coupled inductor design optimization for fast-response low-voltage DC-DC converters," in Proceedings of IEEE Applied Power Electronics Conference and Exposition, pp. 817-823 vol.2.

- 13. Singh, B.N. Singh, A. Chandra, K. Al-Haddad, A. Pandey and D.P. Kothari, Oct. 2003, "A review of single-phase improved power quality AC-DC converters" IEEE Trans. on Industrial Electronics, vol.50, no.5, pp.962-981.

- 14. Jih-Sheng Lai, D. Hurst and T. Key, 1991, "Switch-mode supply power factor improvement via harmonic elimination methods," in 6th Annual IEEE Proc. on Applied Power Electronics Conference and Exposition, APEC'91, pp. 415-422.

- 15. S. Singh, G. Bhuvaneswari and B. Singh, 2010, "Design, modeling, simulation and performance of a MOSMPS fed from a universal standard Single-phase outlet," in Int. Conf. on Power Electronics, Drives and Energy Systems(PEDES) & Power India, pp. 1-6.

- 16. Shikha Singh, G. Bhuvaneswari and Bhim Singh, 28th-30th January 2011, "Power quality improvements in multioutput forward boost converter," in IEEE Conf. on India International Conference on Power Electronics (IICPE), NSIT Delhi, pp. 1-5.

- 17. Shikha Singh, Vashist Bist, Bhim Singh and G. Bhuvaneswari, 2014, "Power factor correction in SMPS for computers using canonical switching cell converter," IET Power Electronics, vol. 8, no.2, pp. 234-244.

- 18. A. Fardoun, E.H. Ismail, A. J. Sabzali and M.A. Al-Saffar, July 2012, "New efficient bridgeless Cuk rectifiers for PFC applications," IEEE Trans. on Power Electronics, vol. 27, no. 7, pp. 3292-3301.

- 19. J. Sabzali, E. H. Ismail, M. A. Al-Saffar and A. A. Fardoun, March/April 2011, "New bridgeless DCM Sepic and Cuk PFC rectifiers with low conduction and switching losses," IEEE Trans. Industry Applications, vol. 47, no. 2, pp. 873-881.

- 20. M. Mahdavi and H. Farzanehfard, April 2014, "Zero-voltage transition bridgeless single-ended primary inductance converter power factor correction rectifier," IET Power Electronics, vol.7, no. 4, pp.895-902.

- 21. Jae-Won Yang and Hyun-Lark Do, July 2013, "Bridgeless SEPIC converter with a ripple-free input current," IEEE Trans. Power Electronics, vol. 28, no. 7, pp. 3388-3394.

- 22. Hong Mao, J. Abu-Qahouq, Shiguo Luo and I. Batarseh, July 2004, "Zero-voltage-switching half-bridge DC-DC converter with modified PWM control method," IEEE Trans. Power Elect., vol. 19, no. 4, pp. 947-958.

- 23. D.S.L. Simonetti, . Sebastian and . Uceda, 1997, "The discontinuous conduction mode Sepic and Cuk power actor preregulators: analysis and design," IEEE Trans. Ind. Electronics, vol. 44, no.5, pp. 630-637.

- 24. V. Vlatkovic, D. Borojevic and F. C. Lee, "Input filter design for power factor correction circuits," IEEE Trans. Power Electronics, vol.11, no.1, pp. 199-205.

- 25. Limits for Harmonic Current Emissions, International Electro technical Commission Standard, 61000-3-2, 2004.

- 26. Pit-Leong Wong, Peng Xu, P. Yang, and F.C. Lee, 2001, "Performance improvements of interleaving VRMs with coupling inductors," IEEE Trans. on Power Electronics, vol. 16, no. 4, pp. 499-507.

- 27. M. Schultz and C. R. Sullivan, March 26, 2002, "Voltage converter with coupled inductive windings, and associated methods," U.S. Patent 6,362,986.

- 28. Jieli Li, Charles R. Sullivan, Aaron Schultz, APEC 2002, "Coupled inductor design optimization for fast-response low-voltage DC-DC converters," in Proceedings of IEEE Applied Power Electronics Conference and Exposition, pp. 817-823 vol.2.

- 29. Peng Xu, Jia Wei, Kaiwei Yao, Yu Meng, F.C. Lee, APEC 2002, "Investigation of candidate topologies for 12 V VRM," in Proceedings of IEEE Applied Power Electronics Conference and Exposition, pp. 686-692 vol.2.

- 30. A.V. Ledenev, G.G. Gurov, and R.M. Porter, April 8, 2003, "Multiple power converter system using combining transformers," U.S. Patent 6,545,450.

# Author' biography with Photo

P.Karpagavalli received B.E. . degree in Electrical Engineering from the Annamalai, University, chidambram in 1994 and M.E Degree in Power electronics and drives form Anna university, Chennai in 2006.and a Ph.D. in Electrical Engineering from Anna University, Chennai, India, in 2015 Since 2001, She has been with Department of Electrical and Electronics Engineering, Government college of engineering, Salem, Tamil Nadu, India, where she is currently a Assistant Professor. Her research interests are in the areas of DC motor control and solid state drives. Mrs.P.Karpagavalli is a life member in ISTE.

SATHIYA M received the B.Tech degree in electrical and electronics engineering from SASTRA university, Thanjavur, Tamilnadu, India in 2015. She is currently pursuing her M.E degree in Power Electronics and Drives from Government College of Engineering, Salem, Tamilnadu, India. Her area of interest includes interleaved and bridgeless converter design, multilevel inverter design.