# Performance Optimization and Comparison of CNT Interconnect with Copper at VDSM Technology

Kureshi Abdul Kadir and Mohd. Hasan

Vishwabharati Academy's College of Engineering Ahmednagar, University of Pune (M.S),India

akkureshi@rediffmail.com

Dept. of Electronics Engineering, Aligarh Muslim University, Aligarh (U.P), India

Mohd.hasan@amu.ac.in

### **ABSTRACT**

As the CMOS process technology continues to scale, standard copper (Cu) interconnect will become a major hurdle for the best performance at very deep submicron (VDSM) technology node. The carbon nanotube (CNT) bundles have potential to provide an attractive solution for the higher resistivity and electromigration problems faced by traditional copper interconnects in VDSM technology node. This paper presents important guidelines to minimize the resistance, capacitance and inductance of a mixed CNT bundle interconnect for achieving best performance. The performance of mixed CNT bundle and copper is then compared at local and global interconnects level at 22nm technology node. HSPICE simulations carried out using Berkeley predictive technology model (BPTM) at an operating frequency of 1GHz, shows that for interconnect length of 1000um, the mixed CNT and optimized CNT (CNT\_Opt) bundles are 1.98X and 2.20X faster, 74% and 84% more energy efficient respectively than the Copper interconnects.

# Indexing terms/Keywords

Integrated Circuits, VDSM, High Speed, Low Power, Copper Interconnect, Mixed CNT Bundle Interconnect Academic Discipline And Sub-Disciplines

Engineering ; Electronics;

SUBJECT CLASSIFICATION

Digital System

TYPE (METHOD/APPROACH)

Mathematical / Simulation

# Council for Innovative Research

Peer Review Research Publishing System

Journal: International Journal of Management & Information Technology

Vol. 6, No. 2 editor@cirworld.com www.cirworld.com, member.cirworld.com

#### 1. INTRODUCTION

The interconnect cross-sections will become smaller and smaller down to nanometric dimensions in future integrated circuits in very deep submicronera. As interconnect sizes shrink, copper resistivity increases due to grain and surface scattering effects and wires become more and more vulnerable to electromigration [1]-[3]. In order to overcome these limitations, the use of metallic carbon nanotubes (CNTs) as interconnects has been proposed recently [4]-[5]. CNTs can be thought of being made by rolling up a single atomic layer of graphene sheet, to form a seamless cylinder. Depending on the direction in which the CNTs are rolled up (Chirality), they demonstrate either metallic or semiconducting properties [6]. Because of its extremely desirable properties of high mechanical and thermal stability, high thermal conductivity and large current carrying capacity, CNT promises to be a suitable candidate for interconnects of future VLSI circuits in VDSM. However, the high resistance (of the order of 6.45 KΩ) associated with an isolated CNT [7] necessitates the use of a bundle of CNTs. Moreover, due to the lack of control on chirality's, any bundle of CNTs consists of metallic as well as semiconducting nanotubes. Almost all experimental results have demonstrated that a realistic nanotube bundle contains a mixed bundle of single-walled and multi-walled CNTs (SWCNTs and MWCNTs) as shown in Figure. 1 (a) and (b). Depending on the process controls and conditions during CNT synthesis, the diameters of CNTs inside a bundle follow normal distributions [8]-[10]. A SWCNT consists of one graphene shell. If several SWCNTs with varying diameters are nested concentrically inside one another, the resulting structure is called as MWCNT. The MWCNT has multiple shells. Recent findings have shown that all shells in an MWCNT can conduct if they are properly connected to the contact and hence lead to very low resistance [11]-[12]. This paper investigates the prospects of a mixed bundle of CNTs as interconnect for future VDSM applications. To the best of our knowledge, this is the first effort to optimize and then compare the transmission line model interconnects parameters of mixed bundle of CNTs with that of copper wire. We compare interconnect parameters and performance of CNT bundle and Copper interconnect at Local and Global levels.

Figure.1 (a) Single Walled Carbon Nanotube (SWCNT)

(b) Multi-Walled Carbon Nanotube (MWCNT)

The investigations have been based on simulation runs with Carbon Nanotube Interconnect Analyzer (CNIA) [13] and Berkeley Predictive Technology Model [14] tools, based on the interconnect geometries suggested in [15] for 22nm CMOS high performance transistor model of [16]. The rest of the paper is organized as follows. In section II, resistance of mixed bundles of CNTs is analyzed and optimized with respect to the tube diameter and tube density. Section III and section IV discuss the CNT inductance and capacitance optimization respectively. Section V then compares the performance of mixed CNT bundle and Cu interconnects and section VI concludes this paper.

#### 2. ANALYSIS OF CNT BUNDLE RESISTANCE

The resistance of an MWCNT or SWCNT is determined by two factors: the conducting channels per shell and the number of shells. A SWCNT consists of one shell whereas MWCNT consists of several shells as shown in Figure. 1(b). The number of shells (Nshell) in MWCNT is determined by the outer diameter (Douter) and inner diameter (Dinner) of the tube [17].

Nshell = 1+ (Douter - Dinner) /

$$2\delta$$

(1)

Where  $\delta$  is the Vander Waals distance (0.34nm). The number of conduction channel per shell [9] is given by

Nchan/shell =

$$(a.di + b)$$

. pm  $d \ge 6nm$  (2)

2. pm d < 6nm

Where a = 0.1836 nm<sup>-1</sup>, b = 1.275, 'di' is the shell diameter and 'pm' is the probability of the tube being metallic.

Any conducting channel provides either intrinsic resistance (Ri) or ohmic resistance (R0) according to the CNT length. The diameter dependant channel resistance for one shell, as given in [17] is

Rshell (di,

$$I$$

) = Ri / Nchan/shell  $I \le \lambda$  (3)

R0 / Nchan/shell /> λ

where l is the tube length and  $\lambda$  is the mean free path (MFP). The MFP of any shell depends on the diameter of that shell [18] and is given as

$$\lambda = (\nu F. di / \alpha T) \tag{4}$$

Where ' $\alpha$ ' is the total scattering rate, T is the temperature, and ' $\nu F$ ' is the Fermi velocity of graphene. The channel intrinsic resistance (Ri) is a constant [18] and is given by

$$Ri = h / 2q^2$$

(5)

Where h is the Planck's constant, q is the charge of an electron.

The ohmic resistance depends on the diameter of shell and tube length [18] and is given by

$$R0 = (h / 2q^2) (I/\lambda) = Ri (I/\lambda)$$

(6)

Since the resistance of a single CNT (SWCNT or MWCNT) is very high, therefore, a bundle of CNTs is used as interconnect, it provides overall lower resistance than copper [19]-[20].

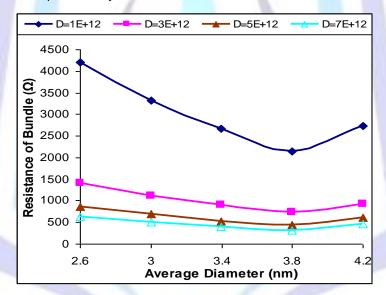

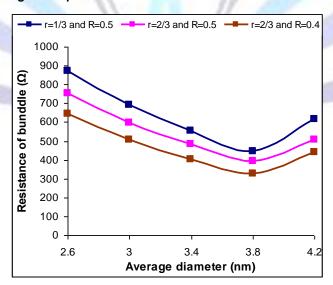

The mixed bundle of CNTs has been analyzed with respect to the average diameter and density of the CNTs in the bundle. Figure. 2 shows the variation in the resistance of a 200µm long mixed bundle of CNTs with change in the average diameter and density of tubes. As the diameter increases, the number of shells also increases as per equation 1, which in turn gives rise to larger number of conduction channel (N). Hence, the bundle resistance decreases as per equation 3. However, beyond a point (in this case, diameter=3.8nm), increase in diameter results in the rise of resistance. This is because when the diameter is increased, the CNTs comes closer to each other as shown in Figure. 3, but the total number of tubes in the bundle remains constants. When the diameter is further increased, the number of tubes in the bundle of a given cross-section reduces, thereby, increasing the overall resistance of the bundle. As the density of the bundle increases, the bundle can accommodate more CNTs, therefore the resistance of the bundle is inversely proportional to the density of CNTs in the bundle. It is clear from above observations that the diameter of the tubes and the tube density in a bundle can be optimized to yield the minimum bundle resistance.

Figure.2 Average diameter vs. bundle resistance

Figure.3 Tube density vs. CNT to CNT spacing

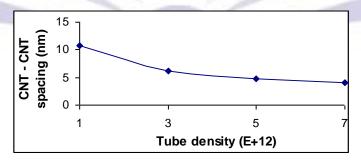

Figure. 4(a) shows simulation results of realistic tube density of 5E+12 tubes/cm<sup>2</sup> [12] with the probability (r=1/3) of the metallic tube for interconnect length of 200um. As the diameter is increased from 2.6nm to 3.8nm, the number of CNTs in a bundle remains constant equal to 130 as shown in Figure 4(b) with CNT to CNT spacing of 4.8nm and the number of conduction channel (N) increases from 236 to 372 as shown in Figure 4(c), therefore the bundle resistance decreases by 49% from  $872\Omega$  to  $447\Omega$ . If the diameter is further increased to 4.2nm, the bundle only accommodates 120 CNTs, therefore, 'N' drops from 372 to 272 and bundle resistance increases from  $447\Omega$  to 616  $\Omega$  (increase of 38%). Hence, the optimum selection of diameter decides the bundle resistance.

Figure. 4 (a) Resistance of bundle, (b) Number of CNTs and (c) Number of channels vs. Avg. diameter

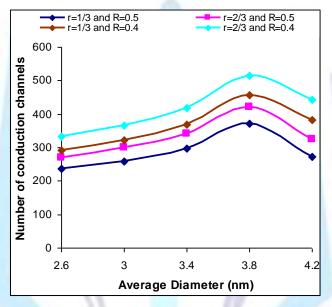

Figure.5 Optimization of number of conduction channels

Figure.6 Optimization of resistance of CNT bundle

Similarly, the high value of metallic tube ratio 'r' in the bundle increases its conductance. The ratio (R) = Dinner/Douter impacts the bundle conductance through changing the number of shells. A smaller 'R' value leads to more shells and therefore, higher conductance [21]. As shown in Figure. 5 and 6,the optimized bundle of diameter 3.8nm with process

parameter of (R=0.4 and r=2/3) compared to (R=0.5 and r=1/3) provides 38% and 27% improvement in number of conduction channels and bundle resistance respectively.

# 3. ANALYSIS OF CNT BUNDLE INDUCTANCE

The CNT has two types of inductances namely magnetic and kinetic. The magnetic inductance depends on the magnetic field inside and between the tubes whereas the kinetic Inductance is the kinetic energy of electrons, which is per unit length for each conduction channel in a CNT shell. The kinetic inductance per conduction channel is given by [22]

$$Lk = h L / 4e^2 vf N$$

(7)

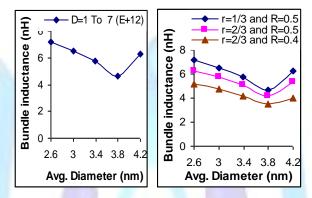

Where 'h' is Planks constant, 'e' is the charge of single electron, 'vf' is the Fermi velocity in graphite, and 'L' is the length of CNT. This shows that the kinetic inductance of a bundle is inversely proportional to number of conduction channels 'N'. As per discussion in section II, by lowering 'R' we can create more shells and hence lower the kinetic inductance.

Figure.7 Inductance and optimized inductance of CNT bundle

The bundle inductance is the sum of magnetic and kinetic inductance. The kinetic inductance of CNT bundle is much larger than the corresponding magnetic inductance (which is in the range of pH/µm). Therefore, the magnetic inductance can be neglected in evaluating the total inductance of the bundle. Results show that the variation in average diameter affects the inductance similar to the resistance. However, variation in tube density has no effect on the dominating 'Lk' as the number of conduction channels remains independent of density as shown in Figure. 7.

#### 4. Analysis of CNT bundle capacitance

The capacitance of a CNT arises from two sources: The electrostatic capacitance (CE) and the quantum capacitance (Cq) [23]. The capacitance 'CE' is calculated by treating the CNT as a thin wire, with diameter 'D', placed at a distance 'y' away from a ground plane. It is defined as follows:

CE =

$$2\pi\epsilon/\ln(y/D)$$

(8)

Whereas the quantum capacitance (Cq) arises from the quantum electrostatic energy stored in the nanotube when it carries the current. Due to Pauli's exclusion principle, it is only possible to add electrons into the nanotube at an available quantum state above the Fermi energy level [22]. The 'Cq' of each shell of a CNT is given by

$$Cq = {4e^2 / h vf} NL$$

(9)

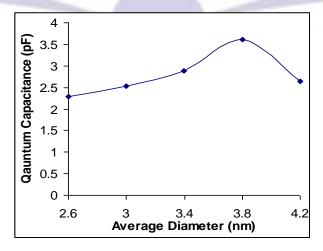

Figure.8 Average diameter vs. quantum capacitance

This shows 'Cq' is directly proportional to 'N' for a given length 'L'. Figure. 8 shows that as the diameter of CNT is increased, the quantum capacitance increases. This is due to increase in 'N'. It is clear from observation in section II that for diameter higher than 3.8nm, 'N' falls and hence the capacitance 'Cq' decreases. When CNTs carries the current the same effective charge resides on both these capacitance, hence these capacitances appear in series.

# 5. PERFORMANCE COMPARISON

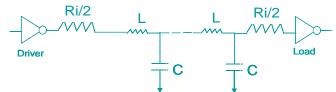

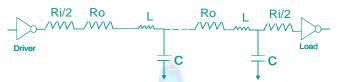

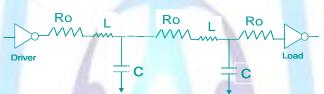

The equivalent circuit parameters of 22nm technology node are extracted using [13] and [14] tools for CNT bundle and Cu interconnects respectively. The interconnect dimensions for year 2016 [15] for local and global interconnects are listed in Table I and the extracted RLC parameters are reported in Table II to IV. The optimized RLC parameters of CNT interconnects (CNT\_Opt) are obtained by selecting (r=2/3, R=0.35, d=3.8nm and D=5E+12 tubes/cm²) as discussed in section II, whereas the normal parameters are obtained by selecting (r=1/3, R=0.5, d=3.8nm and D=5E+12 tubes/cm²) respectively. We use standard test benches [23]-[24], shown schematically in Figure. 9 to Figure. 11 for performance analysis and comparison of CNT bundle and Cu interconnects in terms of power dissipation and delay.

Table I. Interconnect technology parameters

| Technology<br>Node | Local interconnect |             | Global interconnect |             |

|--------------------|--------------------|-------------|---------------------|-------------|

|                    | Width<br>(nm)      | Height (nm) | Width<br>(nm)       | Height (nm) |

| 22nm (2016)        | 22                 | 44          | 33                  | 85.8        |

Table II. RLC parameters of Cu Interconnect

| Interconnect le | ength (um) | R (Ω) | L(pH) | C(fF)) |

|-----------------|------------|-------|-------|--------|

| Local           | 0.5        | 11.36 | 0.25  | 0.0664 |

|                 | 1          | 22.75 | 0.51  | 0.1330 |

| Global          | 200        | 1554  | 344   | 34.77  |

| - 0             | 1000       | 7770  | 2460  | 173.85 |

Table III. RLC parameters of CNT Interconnect

| Interconnect le | ngth (um) | R (Ω) | L(pH) | C(fF)) |

|-----------------|-----------|-------|-------|--------|

| Local           | 0.5       | 21.56 | 11.08 | 0.0640 |

|                 | 1         | 21.60 | 22.12 | 0.1280 |

| Global          | 200       | 447   | 4670  | 29.84  |

|                 | 1000      | 2235  | 23710 | 149.22 |

Table IV. RLC parameters of optimized CNT Interconnect

| Interconnect le | ength (um) | R (Ω) | L(pH) | C(fF)) |

|-----------------|------------|-------|-------|--------|

| Local           | 0.5        | 13.65 | 7.25  | 0.0641 |

|                 | 1          | 13.74 | 14.85 | 0.1281 |

| Global          | 200        | 301   | 3150  | 29.91  |

|                 | 1000       | 1508  | 16110 | 149.60 |

In Figure.9 to Figure.11 'Ro' represents ohmic resistance, 'L' represents total inductance and 'C' represents total capacitance of interconnects. However, for Local interconnects, the resistance of CNT bundle is higher because of smaller number of tubes accommodated in the bundle geometry. Moreover, the resistance of CNT Local interconnect remains independent of length because the maximum length of local interconnects considered in our analysis is 1µm which is smaller than the mean free path (MFP) of CNTs. For CNTs length less than its MFP, electron transport is essentially

ballistic within the nanotube and the resistance is independent of length [19]. Therefore, intrinsic resistance (Ri) associated with any CNT bundle cannot be avoided and is equally divided between the two contacts on either side of the bundle, as shown in Figure. 9 and Figure. 10.

Figure. 9 CNT bundle model for Local interconnect

Figure. 10 CNT bundle model for Global interconnect

Figure. 11 Copper wire model for Local and Global interconnects

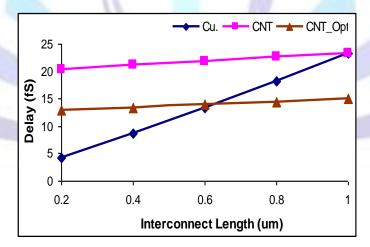

The driver for local interconnect is assumed to be a minimum sized inverter driving a fan-out of four (FO4) minimum sized inverters at the load end. For global interconnects, the driver and load devices are sized up. The performance of interconnects is analyzed by using the extracted equivalent circuit parameters, reported in Table II to IV in the respective test bench. The delay of interconnect is measured as the time taken by the signal to reach from output of the driver to the input of FO4 load. As 'Ri' of CNT local interconnects is constant, therefore, it provides constant delay. Hence, compared to Cu, the CNT interconnect has delay penalty. However, the optimized CNT (CNT\_ Opt) provides more numbers of shells and 1.54X more conduction channels than the unoptimized CNT, therefore for longest local interconnect length of 1um, the CNT\_Opt is 36% more faster than the Cu interconnect as shown in Figure. 12.

Figure.12 Delay of local interconnect

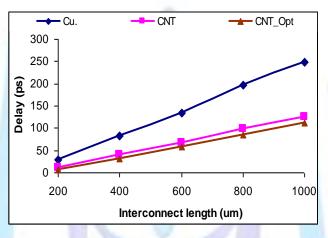

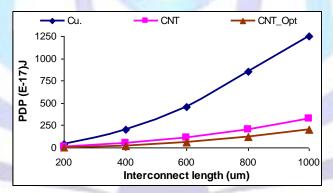

As the capacitance of CNT interconnect is smaller than copper and therefore, for a length of 1um, the CNT\_Opt is 62% more energy efficient than the Cu interconnect, which is shown in Figure. 13. Compared to copper, the speed advantage of CNT bundle for global interconnect is more, this is due lower resistance of CNT bundle attributed because of smaller value of scattering or ohmic resistance 'Ro'. For interconnect length of 1000um, the CNT and CNT\_Opt is 1.98X and 2.20X faster, 74% and 84% more energy efficient than the Copper interconnect respectively as depicted in Figure. 14 and Figure. 15.

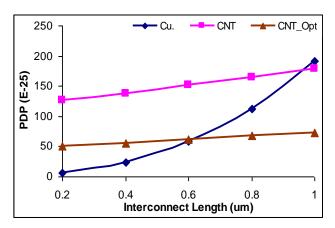

Figure.13 Power delay product of local interconnect

Figure.14 Delay of Global interconnect

Figure.15 Power delay product of Global interconnect

## 6. CONCLUSIONS

This paper presents a comprehensive analysis and optimization of mixed CNT bundle interconnects and investigates their prospects as a low power high speed interconnects for future very deep submicron technology. The propagation delay and power dissipation analysis of CNT interconnects have been performed on standard test benches after optimization of their key parameters. It has been observed that for global interconnects, mixed bundle of CNTs consume lower power than its Cu counterpart. Similarly the mixed CNT bundle global interconnects are faster despite having larger inductances because of the lower values of delay dominating components namely 'R' and 'C' as compared with Copper. Although at lower values of local interconnect lengths, the CNT has delay and power penalties, but the CNT\_Opt is faster and more power efficient than traditional Cu interconnects for local interconnect lengths longer than 0.6um. Our analysis results also point out that the selection of tube density, tube distribution, metallic tube ratio, the ratio of Dinner/Douter and bundle dimensions are crucial factors in determining the conductance, inductance and capacitance of a mixed CNT bundle. This paper provides important guidelines for the selection of these key parameters to design mixed CNT bundles interconnect for future applications in very deep submicron technology.

#### REFERENCES

- W. Steinhogl et al, "Comprehensive study of the resistivity of Copper wires and lateral dimensions of 100nm and [1] smaller", Journal of Applied Physics, Vol. 97, 023706, 2005.

- International Technology Roadmap for Semiconductors, 2005, Online Available: http://public.itrs.net

- A. Naeemi, et al., "Performance Comparison between Carbon Nanotube and Copper Interconnects for Gigascale [3] Integration (GSI)", IEEE Electron Device Letters 2005, Vol. 26, No. 2, pp. 84-86.

- J. Li, et al, "Carbon Nanotube Interconnects: A Process Solution", IEEE International Interconnect Technology [4] Conference, pp. 271-272, 2004.

- A. Naeemi, et al, "On-chip Interconnect Networks at the end of the roadmap: Limits and Nanotechnology [5] Opportunities", IEEE Int. Interconnect Tech. Conf., pp. 201-203, 2006.

- J. W. Mintmire et al, "Universal Density of State for Carbon Nanotubes", Physical Review Letters, Vol. 81, No. 12, [6]

- Paul L. McEuen, et al, "Single-Walled Carbon Nanotube Electronics", IEEE Transactions Nanotechnology, Vol. 1, [7] No.1, pp. 78-85, 2002.

- [8] M. Nihei, D. Kondo, A. Kawabata, S. Sato, H. Shioya, M. Sakaue, T. Iwai, M. Ohfuti, and Y. Awano, "Lowresistance multi-walled carbon nanotube vias with parallel channel conduction of inner shells," in Proc. IEEE Int.Interconnect Technol. Conf., Jun. 2005, pp. 234–236.

Naeemi, A., and Meindl, J.D., "Compact physical models for multiwall carbon-nanotube interconnects", IEEE

- [9] Electron DeviceLett., 2006, 27, (5), pp. 338-340

- C. L. Cheung, A. Kurtz, H. Park, and C. M. Lieber, "Diameter-controlled synthesis of carbon nanotubes," J. Phys. Chem., Vol.106, No.10,pp. 2429-2433, 2002.

- Li. H.J., et al., "Multi-channel ballistic transport in multiwall carbon nanotubes". Phys. Rev. Lett., 2005 [11]

- [12] S. Haruehanroengra and Wei Wang, "Analyzing conductance of mixed carbon-nanotube bundles for interconnect applications", IEEE Electron Device Lett., Vol.28, No.8, August 2007, pp. 756-759

- [13] http://www.nanohub.org/tools/

- [14] http://www.eas.asu.edu/~ptm/

- [15] Arthur Nieuwoudt, et al., "Predicting the perforance and reliability of future field programmable gate arrays routing architecture with carbon nanotube bundle interconnect", IET Circuits devices systems, Vol.3, No.2, 2009,

- http://www-device.eecs.berkeley.edu/~bsim3/bism4

- S. Haruehanroengra and Wei Wang, "Analyzing conductance of mixed carbon-nanotube bundles for interconnect applications", IEEE Electron Device Lett., Vol.28, No.8, August 2007, pp. 756-759

- A. Nieuwoudt et al., "Evaluating the Impact of Resistance in Carbon Nanotube Bundles for VLSI Interconnect using Diameter dependant Modeling Techniques", IEEE Trans. Electron Devices, Vol. 53, No. 10, pp. 2460-2466,

- A. Svizhenko, M. P. Anantram, and T. R. Govindan, "Ballistic transport and electrostatics in metallic carbon [19] nanotubes," IEEE Trans. Nanotechnol., vol. 4, no. 5, pp. 557-562, Sep. 2005.

- L. Forró and C. Schönenberger, "Physical properties of multi-wallnanotubes," in Topics in Applied Physics, [20] Carbon Nanotubes: Synthesis, Structure, Properties and Applications, M. S. Dresselhaus, G. Dresselhaus, and P. Avouris, Eds. Berlin, Germany: Springer-Verlag, 2000.

- [21] M. Nihei, D. Kondo, A. Kawabata, S. Sato, H. Shioya, M. Sakaue, T. Iwai, M. Ohfuti, and Y. Awano, "Lowresistance multi-walled carbon nanotube vias with parallel channel conduction of inner shells," in Proc. IEEE Int.Interconnect Technol. Conf., Jun. 2005, pp. 234-236.

- Arthur Nieuwoudt and Yehia Massoud, "On the optimal design, performance and reliability of future carbon nanotub-based interconnect solutions", IEEE Trans. Electron devices, Vol.55, No.8, August 2008, pp. 2097–2110

- P. J. Burke, et al., "Luttinger Liquid Theory as a Model of the Gigahertz Electrical Properties of Carbon Nanotubes", IEEE Transactions Nanotechnology, Vol. 1, No. 3, pp. 129-144, 2002.

- [24] S. M. Kang and Yusuf Leblebici, "CMOS Digital Integrated Circuits (Analysis and Design)", 3rd ed. McGraw-Hill 2007.