# Performance Analysis and FPGA Implementation of Digital PID Controller for Speed Control of DC Motor

Charul Agarwal<sup>1</sup>, Ashutosh Gupta<sup>2</sup>, Haneet Rana<sup>3</sup>

<sup>1</sup>M.Tech ECE Scholar, Amity University, Noida, er.charulagarwal@gmail.com

<sup>2,3</sup>Assistant Professor, Amity University, Noida

## **Abstract**

This paper deals with the performance analysis and implementation of PID(Proportional-Integral-Derivative) Controller on FPGA platform. The hardware implementation has been done on Xilinx Spartan 3E FPGA board. The software implementation has been done using Xilinx ISE 8.1 i as a tool and simulation is performed using ModelSim 5.4a as a simulator. The PWM signal is generated by FPGA board, which further given to dc motor for its speed control. A new technique has been introduced for the generation of the control input as a PWM signal for controlling the motor driver circuit and decoding the optical encoder data for using it for the speed feedback in the PID control loop. The VHDL algorithm for the proposed implementation has been presented in this paper. Performance analysis of PID controller using MATLAB software shows the effectiveness of the proposed method.

Keywords: FPGA, Digital PID controller, PWM Generator, Xilinx Spartan 3E, PMDC Motor.

# Council for Innovative Research

Peer Review Research Publishing System

Journal: INTERNATIONAL JOURNAL OF COMPUTERS & TECHNOLOGY

Vol 7, No 3 editor@cirworld.com www.cirworld.com, member.cirworld.com

#### I. Introduction

Digital controllers have been widely used over the past five decades due to their simplicity, robustness, effectiveness, and applicability for a broad class of systems. Despite the numerous control design approaches that have appeared in the literature, it is estimated that nowadays digital controllers are still employed in more than 95% of industrial processes. An important feature of these controllers is that they do not require a precise analytical model of the system that is being controlled. For this reason, digital controllers have been widely used in robotics, automation, process control, manufacturing, transportation, and interestingly in real time multi tasking applications.[1].

Implementation of digital controllers has gone through several stages of evolution, from the early mechanical and pneumatic designs to the microprocessor based systems but these systems have the drawback of demanding control requirements of modern power conditioning systems will overload most of the microprocessors and the computing speed limits the use of microprocessor in complex algorithms. Microprocessors, Microcontrollers and Digital Signal Processors (DSPs) can no longer keep pace with the new generation of applications that requires more flexible and higher performance without increasing cost and resources. Furthermore the tasks are executed sequentially which takes longer processing time to accomplish the same task in Microcontrollers and DSPs.We have used Digital PID controller in our work.PID controllers have evolved from analog controllers to digital controllers. The analog controllers are mechanical one and digital controller's ranges from microprocessor to SoC platform. The digital domain of control mechanism is less expensive than its analog counterpart; also it is easy to implement the advanced control algorithm. Other advantages of digital domain of control strategies include flexibility in changing parameter, lighter weight and greater insensitivity to noisy external signals[2]. As the growing complexity of motor and motion control applications is increases, it becomes apparent that a reconfigurable hardware such as FPGA offers significant advantage over the microcontroller solutions in the areas of performance, flexibility and inventory control.

Recently, Field Programmable Gate Arrays (FPGA) has becoming alternative solution for the realization of digital control systems. The FPGA based controllers offer advantages such as high speed computation, complex functionality, real time processing capabilities and low power consumption[3]. Hardware Description Languages (HDLs) are used to describe hardware for the purpose of Simulation, Modeling, Testing, Design, and Documentation of digital systems. The most popular HDLs are VHDL [(Very High Speed Integrated Circuit) Hardware Description Language], and Verilog. VHDL is used to describe hardware from the abstract to the concrete level. Many of the Electronic Design Automation (EDA) vendors are standardizing on VHDL as input and output from their tools. These tools include simulation tools, synthesis tools, layout tools and testing tools[4].In the past two years, Spartan II and III FPGA families from Xilinx have been successfully utilized in a variety of applications, which include inverters [5][6], communications [7][8], embedded processors [9], and image processing [10].

#### II. PWM GENERATOR IMPLEMENTATION

Pulse Width Modulation(PWM) is a technique to provide a logic "1" and logic "0" for a controlled period of time. Pulse Width Modulation is used in many applications like controlling the speed of a dc motor. A data register is used to store the value for the counter, this value determines the pulse width. The Up/Down counter is loaded with a new value from the data register when the counter reaches its terminal count; a Toggle Flip-flop generates the PWM output.

When the data value is first loaded, the counter begins to count down from the data value to 0. During this phase of operation the terminal count and PWM signals are low. When the counter transitions through zero, the terminal count is generated and triggers the Toggle flip flop to drive the PWM signal high. The data value is reloaded and counting proceeds upto the maximum value. Again a terminal count will be generated when the counter reaches its maximum value, driving the PWM signal to toggle from high to low. The data value is reloaded and the cycle repeats. The direction of the counter is controlled by the PWM signal: the counter is set to count down when the PWM is low and count up when the PWM is high. The terminal count controls the data value that loads to the counter from the data register. Data is loaded when the terminal count is high. The duty cycle of the PWM signal is controlled by the data value loaded to the up/down counter The duty cycle of the PWM output can be varied by specifying various data values, the higher the data value, higher the duty cycle. In this way, PWM Generator has been implemented.

Table 1: Data values for different duty cycles

| Data Value | Duty Cycle |

|------------|------------|

| 11100110   | 90         |

| 11000000   | 75         |

| 10000000   | 50         |

| 01000000   | 25         |

| 00011001   | 10         |

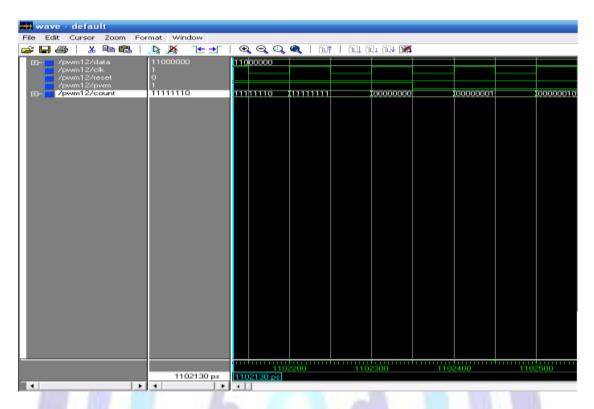

Fig.1 ModelSim Simulator Result for 75% duty cycle

In this way, we have generated PWM signal through ModelSim Simulator. This PWM signal is given as an input to DC motor which helps to drive the motor at different duty cycles..

# III. PID CONTROLLER IMPLEMENTATION

Proportional Integral Derivative (PID) controller is the most preferable controller in industries that does not require precise analytical model of the system to be controlled. PID controllers use a 3 basic behavior types or modes: P - proportional, I - integrative and D - derivative. While proportional and integrative modes are also used as single control modes, a derivative mode is rarely used on it's own in control systems. Combinations such as PI and PD control are very often in practical systems.

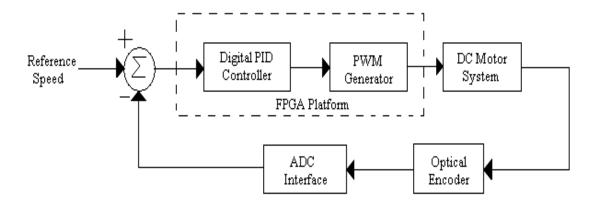

The block level diagram of the system is given in Fig.2.PID Controller and PWM generator have been implemented on FPGA platform. The RPM of the motor is sensed by Optical encoder, this encoder produces a signal with the frequency of the signal directly related to the speed of the motor. Now this signal is fed back to the FPGA platform in a closed loop path. By comparing this feedback signal and reference speed signal, an error signal is generated. This error signal works as an input to the Digital PID Controller. The PID Controller then produces the PWM Command signal based on the reference speed and the actual speed of the motor. So system will produce linear output in accordance with the input signal. The PWM system receives a command signal that will be used to produce the desired percent duty cycle for the DC motor[11].

Fig.2 Block level schematic of the system

....(2)

The general form of PID controller is given as,

$$u(t) = K_p e(t) + K_i \int_0^t e(\tau) d\tau + K_d \frac{de(t)}{dt} \qquad \qquad \dots (1) \label{eq:ut}$$

i.e.

$$U(s) = E(s)[K_p + \frac{K_i}{s} + K_d s]$$

where, K<sub>p</sub>= proportional gain

K<sub>i</sub>= integral gain

K<sub>d</sub>= derivative gain

**Table 2: Motor Parameters Description**

| Motor Parameters | Value                  |

|------------------|------------------------|

| R <sub>a</sub>   | 1Ω                     |

| L <sub>a</sub>   | 0.5 H                  |

| J                | 0.01 kg-m <sup>2</sup> |

| В                | 0.1 N-m-s              |

| K                | 0.01 V/rad/s           |

**Table 3: Controller Description**

| Controller Gains | Value |

|------------------|-------|

| K <sub>p</sub>   | 100   |

| K <sub>i</sub>   | 200   |

| K <sub>d</sub>   | 10    |

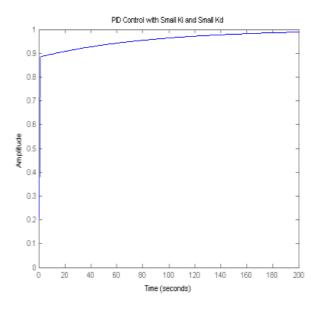

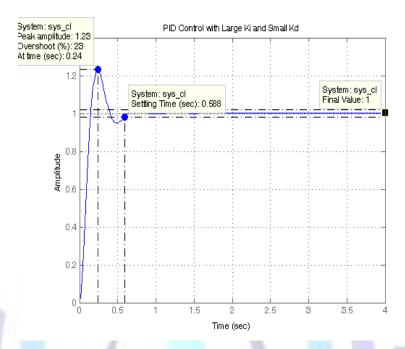

Before implementing PID controller on FPGA, proper gain values must be selected by observing their step responses on MATLAB tool. After that the selected values are used in VHDL code for PID Controller implementation. The PID Controller has been implemented on Xilinx FPGA using the steps given in [14,15].

Fig.3 Step response of PID Controller with small Ki and small Kd.

Fig. 4 Step response of PID Controller with large Ki and small Kd.

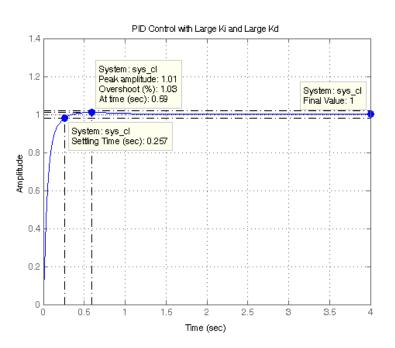

Fig. 5 Step response of PID controller wth large Ki and large Kd.

After seeing all these responses, the response given in fig.5 is the best one to meet the desired specifications.

# IV. OPTICAL ENCODER

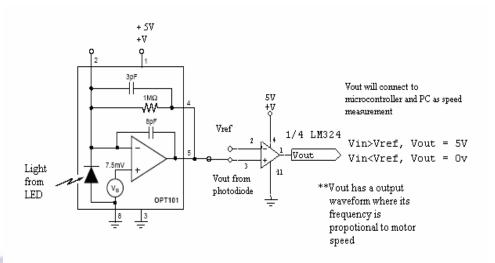

The DC motor has an optical disc (made by cardboard) mounted on its shaft. The disc has N radial lines on its surface. Consider four slots on the disc (N=4). This will give a resolution of 1/4 in one rotation. An LED (light emitting diode) as transmitter is put at one side of the disc and a photodiode, as receiver is fixed on the other side of the disc. Chip OPT 101 is selected as a photodiode.

Chip LM324 is used as a comparator. When the  $V_{out}$  of photodiode is less than  $V_{ref}$ , the output of LM324 will be 0V (Low) and when the  $V_{out}$  is greater than  $V_{ref}$ , the output of LM 324 will be 5V (High). The output signal form LM324 has a frequency which is given by the equation as,

$$f_{out} = \frac{N X RPM}{60}$$

.....(3)

Fig. 6 Optical Encoder Schematic

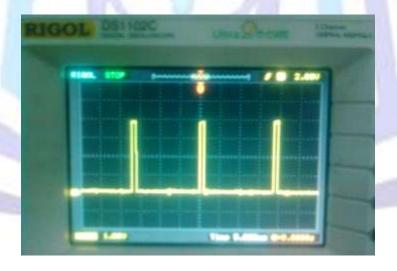

The Vout pin of the optical encoder is connected to the CRO for observing the frequency waveform which is provided to the PID controller through Analog-to-Digital converter (ADC) interface.

Fig.7 Output waveform of Optical Encoder Circuitry

# V. IMPLEMENTATION DETAILS AND EXPERIMENTAL RESULTS

The control algorithm was implemented in a Xilinx Spartan 3E FPGA XC3S250E chip. The average connection delay for the design is 12.006 ns, of which, 66.4% was logic delay and 33.6% was due to route and placing. The maximum frequency of this design is 83.291MHz. The controller, comparator, PWM generator and the encoder interfacing modules have been implemented in the FPGA. The entire system has been implemented using the Xilinx ISE 8.1i as a tool and simulated using ModelSim Simulator 5.4a.

Figure 8 shows the Photograph of the experimental setup and working model of FPGA based DC motor speed control system.

Fig. 8 Experimental setup and working model of FPGA based DC motor speed control system.

#### VI. CONCLUSIONS

The most promising issue regarding with the FPGAs is the fast time to market operation, speed, accuracy and improvement in cost over other digital implementation techniques. Here speed of PMDC motor is controlled by FPGA platform using PID controller. The design shows significant improvements over the present way of implementing digital controllers in Microcontroller Units in terms of latency, response, flexibility, and robustness. It can be extended to accommodate other advanced digital controllers that may also result into superior, reliable and flexible systems.

### REFERENCES

- [1] Sreenivasappa.B.V., Udaykumar.R.Y.,"Design and implementation of FPGA based low power Digital PID controllers" in Proc. ICIIS 2009, 28 31 December 2009, Sri Lanka.

- [2] Hui Hui Chin, All Digit Design and Implementation Of Proportional -Integral- Derivative (PID) Controller, University of Kentucky Master's Thesis, 2006, p.1

- [3] V.Subasri, K.Lavanya and B.Umamaheswari," Implementation of Digital PID controller in Field Programmable gate array (FPGA)"in Proceedings of India International Conference on power electronics 2006.

- [4] Savita Sonoli K.Nagabhushan Raju, Implementation of FPGA based PID Controller for DC Motor Speed Control System, Proceedings of the World Congress on Engineering and Computer Science 2010 Vol II, WCECS 2010, October 20-22, 2010, San Francisco, USA.

- [5] R. Jastrzebski, A. Napieralski, O. Pyrhonen and H. Saren, "Implementation and simulation of fast inverter control algorithms with the use of FPGA circuit," Nanotechnology Conference and Trade Show, pp. 238-241, Nanotech 2003.

- [6] Lin. F.S, Chen. J.F, Liang. T.J, Lin. R.L and Kuo, Y.C, "Design and implementation of FPGA-based single stage photovoltaic energy conversion system," Proceedings of IEEE Asia-Pacific Conference on Circuits and Systems, pp 745-748, Taiwan, December 2004.

- [7] Bouzid Aliane and Aladin Sabanovic, "Design and implementation of digital bandpass FIR filter in FPGA," Computers in Education Journal, vol.14, pp. 76-81, 2004.

- [8] M. Canet, F. Vicedo, V. Almenar and J. Valls, "FPGA implementation of an IF transceiver for OFDM-based WLAN," IEEE Workshop on Signal Processing Systems, SiPS: Design and Implementation, pp. 227-232, USA, 2004.

- [9] Xizhi Li and Tiecai Li, "ECOMIPS: An economic MIPS CPU design on FPGA," Proceedings- 4th IEEE International Workshop on System-on-Chip for Real-Time Applications, pp. 291-294, Canada 2004.

- [10] R. Gao, D. Xu and J. P. Bentley, "Reconfigurable hardware implementation of an improved parallel architecture for MPEG-4 motion estimation in mobile applications," IEEE Transactions on Consumer Electronics, vol.49, no.4, November 2003.

- [11] Paul Leisher, Christopher Meyers, FPGA Implementation of a PID Controller with DC Motor Application, System Level Block Diagram, Bradley University Senior Project, 2002, pp.1-3.

- [12] Tukaram Dongale, Subhash Magdum, Kuldip Goilkar, Nilish Chougale, S. R. Ghatage, "FPGA Implementation of a PID controller for dc motor controller application" in proc.IJAIR 2012.

- [13] H. D. Maheshappa, R. D. Samuel and A. Prakashan, "Digital PID controller for speed control of DC motors, IEEE Technical Review Journal, vol. 6, no.3, 1989, pp. 171-176.

- [14]Ashutosh Gupta, Kota Solomon Raju "Design and implementation of 32-bit controller for interactive interfacing with reconfigurable computing systems" International Journal of Computer science & Information Technology (IJCSIT), Vol 1, No 2, November 2009.

- [15] Solomon Raju Kota, Ashutosh Gupta, Shashikant Nayak, Sreekanth Varma, "Module based implementation of Partial Reconfiguration using VHDL on Xilinx FPGA", International Journal of Recent Trends in Engineering, Vol.2, No. 7. November 2009.

- [16] Somsubhra Ghosh, Ranjit Kumar Barai, Samar Bhattarcharya, Prarthana Bhattacharyya, Shubhobrata Rudra, Arka Dutta, Rownick Pyne, "An FPGA Based Implementation of a Flexible Digital PID Controller For a Motion Control System" in Proc. (ICCCI -2013), Jan. 04 06, 2013, Coimbatore, India.

- [17] Mohamed Abdelati, the Islamic University of Gaza, Gaza, Palestine "FPGA-Based PID Controller Implementation".

- [18] I.J. Nagrath and M. Gopal, "Control System Engineering", 5th editions, New Age International Publication, 2003.

#### Author

**Charul Agarwal** completed her **B.Tech (Hons.)** from U.P.T.U, Lucknow in 2008. She is working as an Assistant Professor in Vishveshwarya Group of Institutions, G.B. Nagar and pursues her M. Tech part time degree in Electronics & Communication Engineering from Amity University, Noida. Her interest areas are Microprocessors.

Microcontrollers and FPGAs.